數據采集系統設計

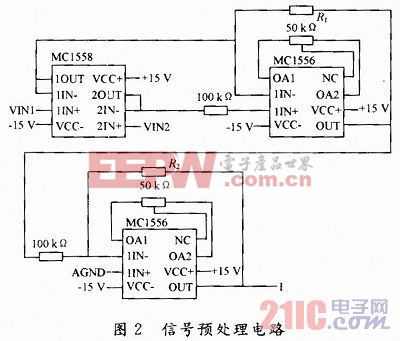

2.1 信號預處理電路

由于待采集電壓信號輸入動態范圍較寬,且極性各異,采用輸入電壓范圍可調的信號預處理電路。信號預處理電路如圖2所示,信號放大倍數為R1×R2/(100×100)。本文引用地址:http://cqxgywz.com/article/194000.htm

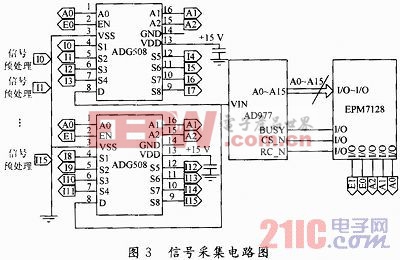

2.2 信號采集模塊

CPLD是在PAL、GAL等邏輯器件的基礎上發展起來的,同以往的GAL、PAL等相比,CPLD的規模比較大,適合于時序、組合等邏輯電路的應用場合。采用Altera公司的EPM7128SQI100作為數據采集的控制芯片,負責信號采樣、A/D轉換、數據輸入控制等。EPM7128SQI100具有128個宏單元,84個用戶I/O管腳,工作電壓為5.0 V,具有2 500個可用門和ISP,管腳間延遲為6.0 ns,計數器速度可高達125 MHz,可以很好地滿足系統的需要。信號采集電路如圖3所示。

ADG508是一款8通道CMOS模擬多路選擇器,具有高速轉換速度和低內阻特性,通道切換具有防短路功能。在CPLD控制下,它可對采集信號進行有序通道切換。A/D轉換芯片選用AD977,AD977是ADI(Analog Devices)公司推出的一款高速16位A/D轉換器,輸入電壓范圍為-10~+10 V,單極5 V電壓供電,采樣頻率可達100kHz。數據采樣系統最大采樣速率可達50kHz,信號分辨率可達0.3mV。通過采用多路轉換開關ADG508與16位A/D配合使用,降低了成本。

評論