一種頻率特性測試儀的設計

摘要:以單片機89C51和可編程邏輯器件(FPGA)為控制中心,設計了一個頻率特性測試儀,用于測試某一特定網絡的頻率響應特性。本系統的主要特點是由FPGA驅動多種串行芯片,在精簡了系統電路結構的同時也不影響程序的效率。其中掃頻信號由AD9851的串行方式產生,擴展了頻率范圍及穩定性。幅度測量由有效值采樣芯片AD637和10住串行A/D轉換器TLV1544配合實現,相位測量采用計數法實現。頻率特性曲線由12位串行雙D/A轉換器TLV5638輸出,并經示波器顯示出來。本系統幅度測量精度達到5%,相位測量精度達到1°。

關鍵詞:掃頻信號;幅度測量;相位測量;串行芯片

頻率特性的測量采用掃頻的方法實現,用AD9851產生掃頻信號,可產生頻譜純凈、頻率范圍廣且穩定度非常高的正弦波。通過二極管負反饋橋式限幅放大電路及有效值采樣電路等實現頻響特性的測量,最后用示波器顯示被測網絡的幅頻特性及相頻特性。

本系統的一個特點是采用了較多串行芯片(AD9851,TLV1544和TLV5638)。為了使電路中的信號干凈,應減少電路連線,采用串行芯片可以有效精簡電路,保證電路的穩定性和減少信號噪聲。但由于串行芯片犧牲了程序的時間效率,所以應該合理設計程序結構。

1 系統方案論證與選擇

1.1 幅度測量電路的設計與論證

方案1:峰值檢波電路。基本的峰值檢波電路是由二極管電路和電壓跟隨器組成,通過電容的充放電實現。此電路測量低頻信號時檢波的紋波較大,適合于測量中高頻率段的信號。

方案2:真有效值檢波。從真有效值檢波的工作原理可以分為線性有效值檢波器、對數有效值檢波器和數字有效值檢波器。典型的真有效值轉換芯片為AD637,使用AD637在測量峰值系數高達10的信號時附加誤差僅為1%,且外圍元件少、頻帶寬。

綜上,選擇方案1。

1.2 相位測量電路的設計與論證

方案1:波形分析法。采用兩片高速A/D轉換芯片同時對輸入的兩路信號進行等時間間隔采樣并將采樣結果分別存儲,然后對所測信號的波形數據進行分析。掃描存儲在RAM中的波形數據,計算兩片A/D轉換器采集兩部分波形數據的最大值或最小值的時間間隔,則信號的相位差為:φx=(Tx/T)x360°其中,Tx為兩路信號相臨極值的時間間隔,T為信號周期。

方案2:計數法。將兩路被測信號經過異或門后,產生一個鑒相脈沖信號,送入FPGA進行記數,計數值為N。若信號頻率為,f,計數頻率為fclk,則相位差為:φx(Nf/fclk)x360°,可判斷被測信號是比標準信號相位超前還是滯后。由于相差在0°~180°之間和360°~180°之間是對稱的,異或后的計數值是相同的,故需加上一極性判別電路。相位的極性判決電路可由D觸發器實現,將兩路信號接D觸發器的D端和CP端,從0端輸出的高低電平可判別相差的極性。

方案1需要用軟件對大量的波形數據進行處理才能達到較高的精度,且采集時間間隔難以精確控制,主要適用于精度要求不是很高的情況。方案2的測量過程可以全部由FPGA實現,AD9851產生的信號頻率f已知,無需測頻,所以這種方法非常容易實現,而且采用FPGA的40 M高頻晶振計數,測量精度和測量范圍都得到提高。因此采用方案2。

2 系統總體設計方案及實現框圖

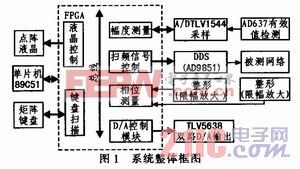

本系統以單片機及FPGA為核心,由掃頻信號源模塊、峰值檢測模塊、限幅放大模塊和相位測量模塊構成。系統框圖如圖1所示。為了提高效率,芯片控制主要由FPGA實現,單片機僅提供系統各模塊的觸發信號。系統工作時,AD9851產生一定頻率的正弦信號,經過被測網絡后,其幅值、相位會有所改變。將被測網絡的輸出端經過AD637有效值檢測電路即得出信號的真有效值,A/D采樣后送于單片機。同時,分別

將被測網絡前后的信號經過限幅放大模塊整形為峰峰值為+5 V的方波,送入FPGA進行相位測量。再改變信號發生器的頻率,測量對應頻率點的相位差與幅度值,直到完成整個頻率段的測試,最后將被測網絡的幅頻特性和相頻特性曲線用示波器顯示出來。

3 主要功能電路設計

3.1 掃頻信號發生器

AD9851是AD公司采用先進CMOS技術生產的具有高集成度的直接數字合成器,可以直接作為信號源,也可通過其內部的高速比較器轉換為方波輸出,作為靈敏的時鐘產生器。它將相位累加器,波形存儲器,10 Bit高速D/A集于一塊芯片中,頻帶寬,頻率精度和穩定度高,外圍電路簡單。

其內部結構如圖2所示。AD9851內部的控制字寄存器首先寄存來自外部的頻率、相位控制字,相位累加器接收來自控制字寄存器的數據后,決定最終輸出的信號頻率和相位,再經過內部D/A轉換器,所得到的就是最終的數字合成信號。

評論