基于USB2_0和DDR2的數據采集系統設計與FPGA實現

2.2 IF模塊設計

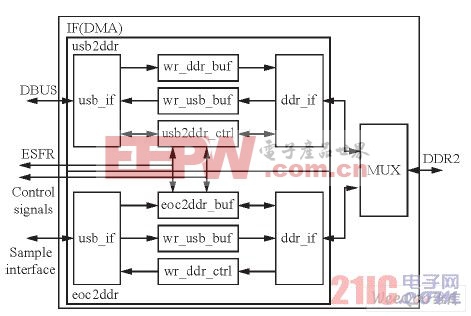

IF模塊負責接口的轉換和數據傳輸的控制,其結構如圖2所示。其中, usb2ddr和eoc2ddr子模塊分別控制USB2.0與DDR2 SDRAM、外部采集接口與DDR2 SDRAM之間數據的上下行傳輸。

上下行數據傳輸分別由usb2ddr_ctrl 和eoc2ddr_ctrl模塊中的狀態機進行控制和管理。其中采集模式和深度由MCU的ESFR總線配置, 而傳輸開始信號則使用MCU的PORT0 [0]、PORT0[1], 結束信號連接在MCU的外部中斷NINT0和NINT1上, 這樣可使MCU能夠及時響應。上行采集開始后, 首先使eoc2ddr_ctrl中的控制狀態機處于寫狀態, 并不斷地比較DDR2的地址與配置深度, 直到采集完成。然后再使usb2ddr_ctrl中的控制狀態機處于讀狀態, 同樣也比較地址與深度,直到數據讀取完成。下行傳輸過程則與之相反。

IF模塊結構框圖

圖2 IF模塊結構框圖。

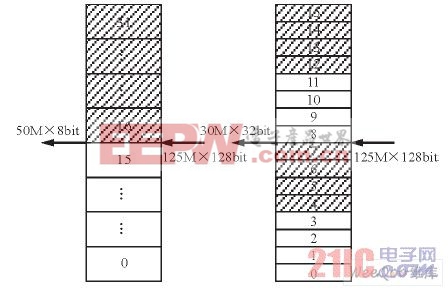

由于各個接口上數據傳輸的速率不同, 因此, 數據傳輸時, 要異步FIFO或者緩存。在本設計中, 由于各接口速率固定, 因此, 可采用雙端口RAM作乒乓緩存方式以提高效率并保證數據連續, 圖3所示是乒乓緩存原理圖。

乒乓緩存原理圖

圖3 乒乓緩存原理圖。

當下行發出數據時, 從DDR2的125 M×128bit到50 M×8 bit所需要的最小深度為32×8 bit, 因為從SDRAM中讀數據的最大延遲是26個DDR2時鐘周期(即208 ns), 而將DDR2讀出的128 bit發出則需要16個時鐘周期(即320 ns), 因此, 為了保證發出的數據可連續進行乒乓操作, 需要2×128bit的深度。同理, 在上行數據從DDR2的125 M×128 bit到USB的30 M×32 bit則需要4×128 bit深度,因為USB時鐘讀完128 bit數據需要133.2 ns, 小于SDRAM 讀數據延遲的208 ns, 因此, 每次從SDRAM中讀2×128 bit數據時, 其乒乓操作就至少需要4×128 bit深度。

3 系統的改進

本數據采集系統對傳統的數據采集系統做了創新型改進。改進主要是三個方面: 一是對數據采集的深度實行可配置模式; 二是在功能上不僅作為數據采集系統, 還能作為數據發生器, 即將采集到計算機上的數據通過數據采集系統發送出來; 三是該數據采集系統有兩種工作模式, 即普通采集模式和觸發采集模式。

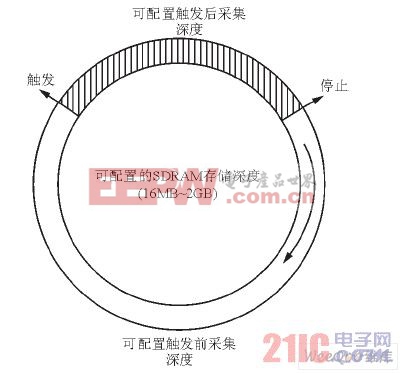

深度可配置增加了系統在使用過程中的靈活性。該系統除了采集數據外, 還能將數據發出來用于芯片的FPGA原型驗證, 從而避免了緩慢的大數據量仿真, 更增強了系統的實用性。通過ESFR配置8 bit的深度寄存器可實現以16 MByte為單位的深度調節。觸發是數據采集系統不可缺少的功能, 因此, 該數據采集系統分為普通采集模式和觸發采集模式。觸發采集模式的原理如圖4所示。在觸發模式中, 可將SDRAM看做一個圓形的循環存儲器, 觸發前后的采集深度同樣也可以通過ESFR配置, 從而實現觸發前后的采集深度比例可調。

觸發實現機制原理圖

圖4 觸發實現機制原理圖。

評論