軟件接收機的GPS信號實時采集方案設計

要在通道13上實現乒乓緩存,需要使用位于0x01A00600和OxOlA0 0618的2個可重新加載RAM參數塊A、B,以及位于外部SDRAM Ox8000 0000~0x8000 0FBF和0x8000 1000~0x8000 1FBF的2個緩沖區BUFl和BUF2。設定A DST=0x8000 0000指向BUFl,RLD=0x0000 0618指向RAM參數塊B,B DST=0x8000 1000指向BUF2,RLD=0x0000 0600指向RAM參數塊B,同時置位每個RAM塊中OPT中的LINK控制位。這樣,當A RAM塊最后一個單元傳輸結束時,會自動加載RLD指向的B RAM塊參數。當下次觸發事件到來時,EDMA就將數據搬移到Ox8000 1000指向的BUF2;相反B RAM塊最后一個單元傳輸結束時,會自動加載RLD指向的ARAM塊參數將后續數據搬移到BUFl,實現乒乓緩存。此外,RAM參數塊A和B的OPT設置為Ox0002 0002,使通道13工作在最高優先級的固定地址到遞增地址的32位一維元素同步鏈接模式。SRC設置為McBSP0 DRR地址0x018C 0000,CNT設置為Ox0000 03FO進行1008個字的單幀傳輸,IDX不影響一維元素的同步傳輸,設置為Ox0000 0000。

為了保持McBSP和EDMA操作的同步性,所有ED-MA通道共享的EDMA-INT在使能通道13前,通過MXL[25:21]映射到可屏蔽中斷INT_8,并置位ICR Bit8清除所有掛起中斷,置位IER Bitl、Bit8使能NMI和INT_8,最后置位全局中斷使能GIE。使能通道13時,需先置位EDMA事件清除寄存器ECRL和中斷掛起寄存器CIPRL Bitl3,以清除先前發生的McBSP0 REVT事件和掛起的中斷信號;然后依次置位EDMA中斷使能寄存器CIERL和通道使能寄存器EERL bitl3,使能通道13和相應的中斷。本文引用地址:http://cqxgywz.com/article/197709.htm

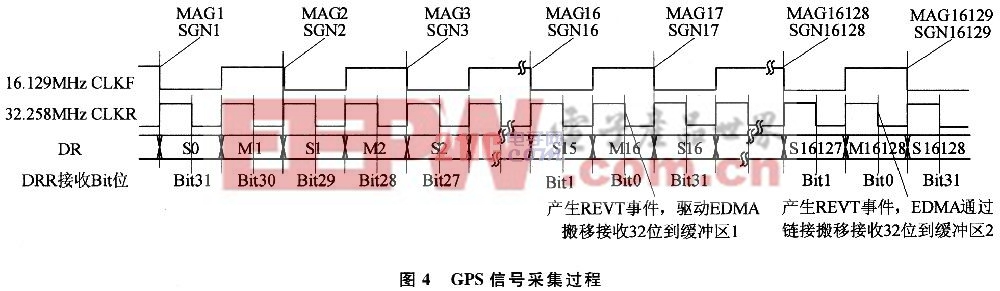

4 采集過程分析

采用基于McBSP、EDMA、SDRAM構成的GPS信號采集方案,主要分為接口配置和信號采集兩個階段。接口配置階段依次完成EMIFA、EMDA、中斷和McBSP0配置,使其工作在一定工作模式下,最后通過置位McBSP接口控制寄存器中的RRST啟動采集過程。信號采集過程基于硬件實現,完全與CPU并發,在ms數據接收完成后與CPU通過中斷INT_8同步數據。具體采集過程如圖4所示。

McBSP32.258 MHz接收時鐘連續32個下降沿接收一個32位字,產生一個REVT事件,對應16.129 MHz射頻采樣時鐘16次下降沿采樣。REVT事件驅動EDMA完成一次DRR 32位接收數據到SDRAM緩沖區搬移,并將CNT減1,緩沖區地址加4指向下一個緩沖單元。假設EDMA當前執行RAM參數A傳輸,那么32.258 MHz接收時鐘1 ms內共32 258個下降沿,可接收1008個32位接收數據,產生1008次REV事件;對應16.129 MHz采樣時鐘16 128次下降沿采樣,共驅動EDMA 1008次32位搬移,占用BUFl Ox8000 0000~0x8000 0FBF 4 032字節空間,CNT減少到O。一旦CNT減小為O,EDMA就觸發INT_8,通知CPU ms數據采集完畢;同時,根據RLD的設定,加載位于0x01A0 0618的參數RAM B到通道13的自身參數RAM。當下次REVT事件到來時,EDMA就執行RAM參數B傳輸,在Ox8000 1000~Ox8000 1FBFBUF2緩沖,此時CPU可處理BUFl中的采集數據。當CNT再次減小到0時,EDMA再次觸發INT_8,通知CPU ms數據采集完畢;同時,根據RLD的設定加載位于0x01A0 0600的參數RAM A到通道13,實現乒乓緩沖。需要注意的是,McBSP RFIG=1工作在幀忽略模式,在第一個CLKF下降沿完成同步后一直忽略后續同步信號,直到32位幀結束才能實現下一幀同步。

結語

本文提出的基于NJl006AK和TSM320C6416的GPS實時信號采集方案,充分利用了DSP內部外設,具有電路簡單可靠、配置方法靈活和CPU同步并發的特點。該方案很好地解決了軟件GPS接收機中數據采集實時性和基帶處理實時性沖突的問題,實現了GPS信號的實時、連續采集,對提升軟件GPS接收機實時性能具有重要意義。

評論