混合同余法產生隨機噪聲的FPGA實現

本文中的FPGA設計平臺選用Altera公司的StratixⅣ芯片EP4SGX230KF40C4ES,開發工具使用Quartus II和Modelsim對其進行功能仿真并觀察仿真結果。

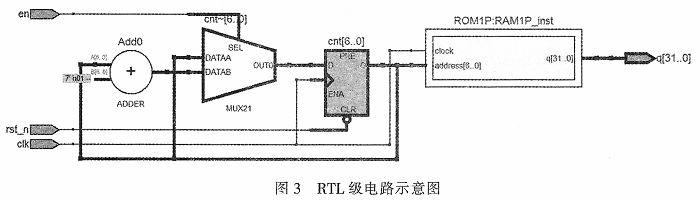

圖3所示為該設計的RTL級電路,從圖中可以看出,電路共有3個輸入信號:使能信號en,復位信號rst_n,時鐘信號clk。該電路的核心是計數器模塊和ROM表模塊。ROM表模塊的實現使用Altera內部的LPM_ROM IP核。電路工作時,由計數器cnt產生地址信號,送給ROM表中進行尋址,在輸出端就可以產生數字高斯白噪聲序列。

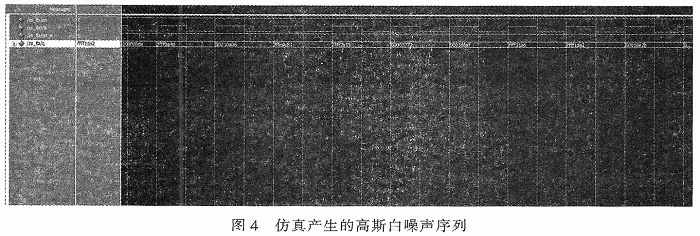

利用Modelsim仿真工具進行仿真,可以觀察到輸出的高斯白噪聲序列,仿真結果如圖4所示。

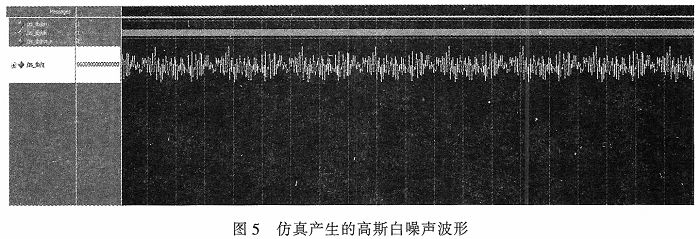

將輸出序列改成模擬形式,可以看到產生的數字高斯白噪聲的波形,如圖5所示。

4 結論

本設計實現的高斯白噪聲發生器電路,工作穩定,并且在PC主控端可以根據不同要求,通過改變均值方差和種子值,從而得到服從正態分布統計特性的不同樣本,進而得到不同種類和滿足不同特性的噪聲。實驗結果產生的高斯白噪聲符合噪聲隨機性和統計特性的要求,本設計可以應用在有源干擾機的工程實踐中,有比較好的實用特性。

評論