生物電阻抗測量系統中弱信號檢測技術研究--正交雙激勵信號檢測方法(二)

3.3正交雙激勵數字相敏檢波方法

本文引用地址:http://cqxgywz.com/article/201610/308726.htm3.3.1正交雙激勵數字相敏檢波原理

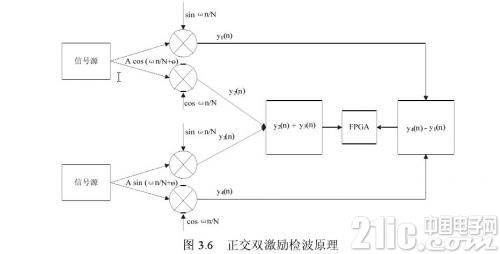

數字相敏檢波技術能夠有效提取被測信號的幅度和相位,隨著累積周期的增加,系統的整體誤差將減小。但是隨著周期的增加,檢波的時間也跟著會增加,以這種方式檢波時,將系統整體誤差減小是以時間為代價換來的。為解決單激勵DPSD存在較大系統誤差的缺點,本文提出一種正交雙激勵數字相敏檢波方法(D-DPSD),其測量原理如圖3.6所示。

正交雙激勵數字相敏檢波方法充分利用激勵源發出的信號的特征,在兩路信號進入被測網絡前確保其正交,即讓余弦激勵信號 通過待測網絡,與一組同頻率正交信號相乘得到y1(n)和y2( n ),然后讓同頻正弦激勵信號通過待測網絡,得到y3( n )和y4( n ),將得到的信號經過線性運算即可消除高頻分量。

通過待測網絡,與一組同頻率正交信號相乘得到y1(n)和y2( n ),然后讓同頻正弦激勵信號通過待測網絡,得到y3( n )和y4( n ),將得到的信號經過線性運算即可消除高頻分量。

3.3.2正交雙激勵數字相敏檢波理論分析

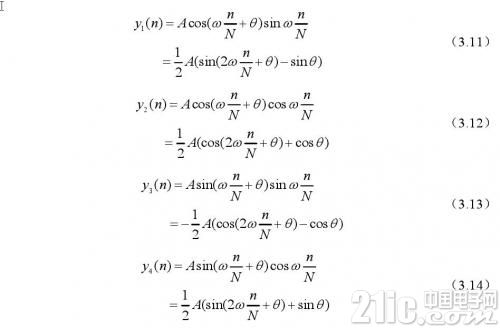

正交雙激勵數字相敏檢波方法是在DPSD算法基礎上提出的,在理論上還延續著DPSD的部分核心思想。例如,D-DPSD還是采用數字正弦波或余弦波進入被測網絡,每路信號通過被測網絡之后還是采用與正交同頻信號相乘的方式解調。不同的是,D-DPSD檢測方式的用兩路保持正交的信號進入被測網絡。首先讓余弦激勵信號 通過待測網絡,與一組同頻率正交信號相乘得到y1(n)和y2( n ),然后讓同頻正弦激勵信號通過待測網絡,得到y3( n )和y4( n ),如下所示:

通過待測網絡,與一組同頻率正交信號相乘得到y1(n)和y2( n ),然后讓同頻正弦激勵信號通過待測網絡,得到y3( n )和y4( n ),如下所示:

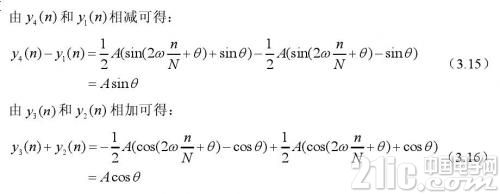

再由(3.15)、(3.16)得到的A sinθ和A cosθ進行以下運算,即可求得目標值θ*和A*:

3.4 DPSD與D-DPSD仿真分析

3.4.1仿真實驗為驗證數字正交鑒幅鑒相結果,在System Generator上搭建了模型系統進行仿真實驗。

System Generator是Xilinx公司的系統級建模工具,在很多方面擴展了MathWorks公司的similink平臺,提供了適合硬件設計的是數字信號處理(DSP)建模環境,加速了、簡化了FPGA的DSP系統級硬件設計,所搭建的系統可直接生產比特流在FPGA中運行。System Generator提供了系統級設計能力,允許在相同的環境內進行軟硬件協同仿真、執行和驗證,并不需要書寫VHDL代碼。在System Generator設計中,利用其強大的信號處理能力,調用各個功能模塊,實現單激勵數字相敏檢波和正交雙激勵數字相敏檢波方法的仿真,其中AD采樣數據經掛接在PLB總線上的IP Core進行處理后傳給System Generator處理單元,數據進入處理單元后首先進行數據類變換,然后分別送入乘法器進行正交相乘運算,將運算結果送到上位機進行處理。

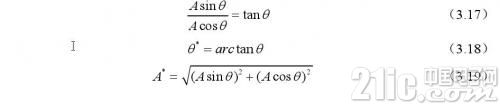

針對本文單激勵數字相敏算法,搭建的仿真系統圖如圖3.7所示。

其仿真結果可以在Wavescope中顯示,也可以通過軟件從文件中調出加以檢測。本文通過MATLAB中的Editor工具調用System Generator中所產生的兩個文件:cos.mat和sin.mat.

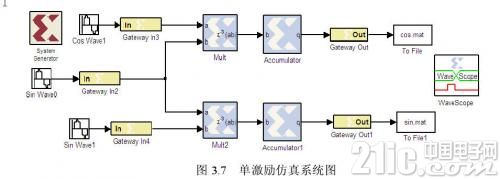

同樣,按正交雙激勵數字相敏檢波方法搭建D-DPSD仿真系統,系統圖如圖3.8所示。

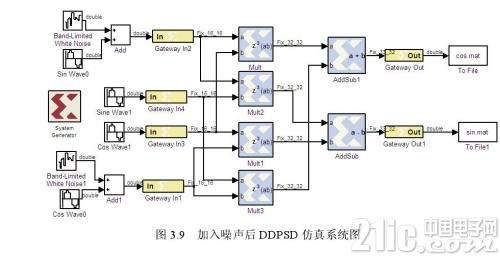

圖3.8為純凈情況下的仿真系統圖,現實情況中,當激勵信號輸入系統時,往往伴有噪聲輸入。搭建仿真系統時,加入白噪聲和隨機噪聲進行仿真,如圖3.9所示。將噪聲加入正、余弦激勵信號Wave0并與Wave0一起輸入系統,與其同頻的一組正交信號Wave1相乘,將最后所得結果存入cos.mat文件和sin.mat文件中,然后再用MATLAB中的Editor工具調用這兩個文件顯示仿真結果。

3.4.2 DPSD與D-DPSD仿真對比

將上一節中搭建的三個系統的輸出結構通過Gateway Out輸出到cos.mat文件和sin.mat文件中,然后再用MATLAB中的Editor工具調用這兩個文件,對其幅度相位進行處理后顯示仿真結果,將其結果顯示為相應的三角函數值。

要提取信號的幅度和相位值,最有效的方法是先提取信號的正弦和余弦值,如果這兩個值在一定數值上平穩,則代表這種方法鑒別信號幅度相位是有效的,越平穩,性能就越高。

3.4.2.1 DPSD仿真分析

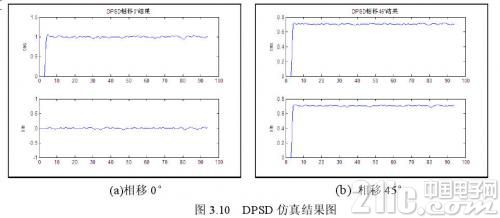

利用圖3.7所示的仿真系統進行仿真,將參數設定為:輸入信號一個周期的量化點數為10,輸入信號的相位偏移分別為0°和45°。可得到結果如圖3.10所示的仿真結果圖。

仿真結果圖中,橫坐標為累加的點數,縱坐標為相應的三角函數值。由圖3.10的仿真結果表明,信號通過網絡后,被提出來的正余弦值與設定相位的正余弦值基本一致,因此這種方法是可行的。

3.4.2.2 D-DPSD仿真分析利

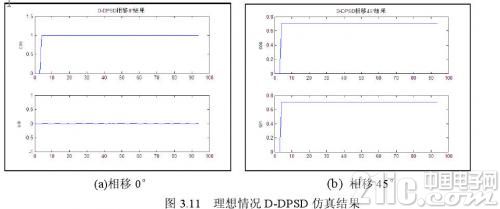

用圖3.8所示的仿真系統進行D-DPSD方法仿真。將參數設定為:輸入信號一個周期的量化點數為10,輸入信號的相位偏移分別為0°和45°。可得到如圖3.11所示的仿真結果圖。

仿真結果表明,信號通過網絡后,被提出來的正余弦值與設定相位的正余弦值一致,因此這種方法可以更精確的計算出信號的幅度和相位。

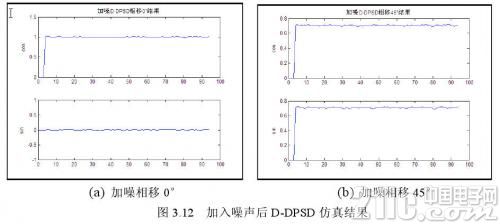

現實情況中,當激勵信號輸入系統時,往往伴有隨機噪聲和白噪聲輸入。運行圖3.9所搭建的仿真系統,得到加噪情況下的仿真結果如圖3.12所示。

仿真結果表明,信號通過網絡后,被提出來的正余弦值與設定相位的正余弦值基本一致,信號平穩,因此這種方法可以得到信號的幅度和相位。

3.4.2.3 D-DPSD與DPSD仿真分析

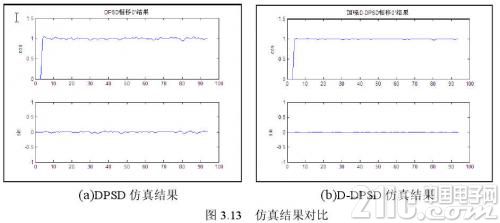

對比D-DPSD算法在DPSD算法基礎上提出,將D-DPSD仿真結果與DPSD在相同條件下的仿真結果進行對比,如圖3.13所示。由圖可知,D-DPSD算法仿真結果明顯平穩,誤差浮動范圍有所減小。因此,D-DPSD減小了DPSD算法累積產生的誤差,從而使整個系統的誤差得到減小,提高了系統測量信號幅度和相位的精度。

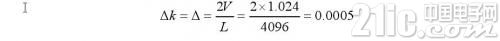

分析測量過程,測量精度主要受AD采樣、乘法器截斷誤差以及累加器截斷誤差影響。只要設計采用12位以上AD進行采樣,并保證差分輸入峰峰值為±1.024V.可計算其量化誤差為:

量化范圍為-V到+V,L為量化間隔數。

為提高測量精度,乘法器和累加器分別采用采用24位和40位,消除截斷誤差的影響,這樣累加器輸出的結果理論誤差為0.0005V,只要保證AD輸入信號幅度較大,系統誤差可以遠小于5%,可滿足生物電阻抗測量要求。

評論