現代電表網絡跨接故障校正方法

商用和住宅應用的電表嚴重依賴基于TIA/EIA-485標準(常稱作RS-485)的長距離、差分數據傳輸網絡。為了克服偏遠總線節點之間常遇到的大接地電勢差問題,在信號和電源線路方面,所有節點均與本地電表電路進行電隔離。

本文引用地址:http://cqxgywz.com/article/201610/309106.htm電表網絡是一種典型的主/從系統,其主節點(放置在控制中心內)的主機處理器按序對總線上的多個從節點(位于單個終端客戶的營業場所內)進行尋址。

單個網絡通常由多達60個節點組成,因此如果在網絡安裝期間沒有預防措施或者網絡工作期間沒有相應糾正辦法的話,雙絞線總線的兩條導線發生意外跨接的可能性非常高。

美國和歐洲的各大電表公司主要依靠經過嚴格培訓的網絡安裝人員,并利用視覺區分方法,即以不同顏色標示線纜作為防止跨接的措施。這種方法允許使用標準收發器和線纜,例如:隔離式RS-485收發器和5類線纜。

為了進一步降低接線錯誤的風險,最近的一些網絡設計紛紛使用一種被稱作訓練序列的方法,它讓從節點適應主節點的信號極性。在這種序列中,主節點向所有從節點廣播一種獨特的位模式。最初于上電期間存儲在每個從處理器內的相同位模式,與主節點所發送的模式進行比較。如果模式匹配,則從節點保持其信號極性。如果不匹配,則從處理器反轉接收數據和發送數據的信號極性。這種反轉通常通過從處理器內的互斥或(Exclusive-OR)函數來完成,并不要求對硬件設計進行任何修改。因此,仍然維持了標準收發器的正常工作。

與這種方法形成對比的是,亞洲電表公司推動發展更為低成本的網絡設計,它們利用:

l 經驗不足的網絡安裝人員

l 低成本、非顏色編碼線,而非雙絞線

l 具有集成信號極性校正的專用收發器

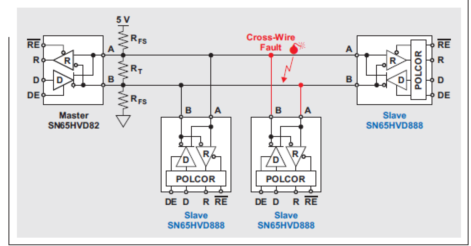

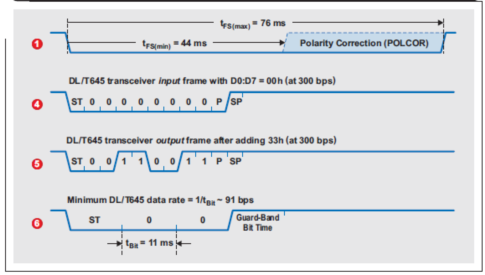

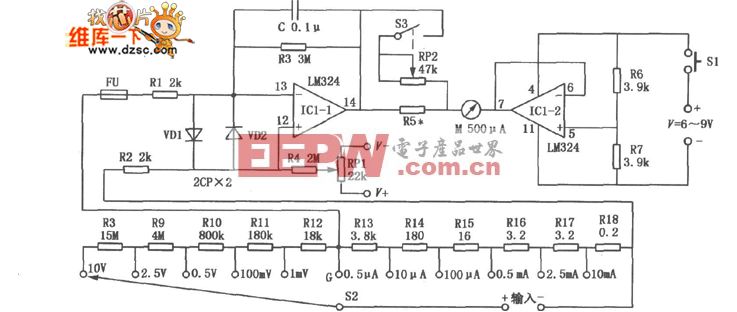

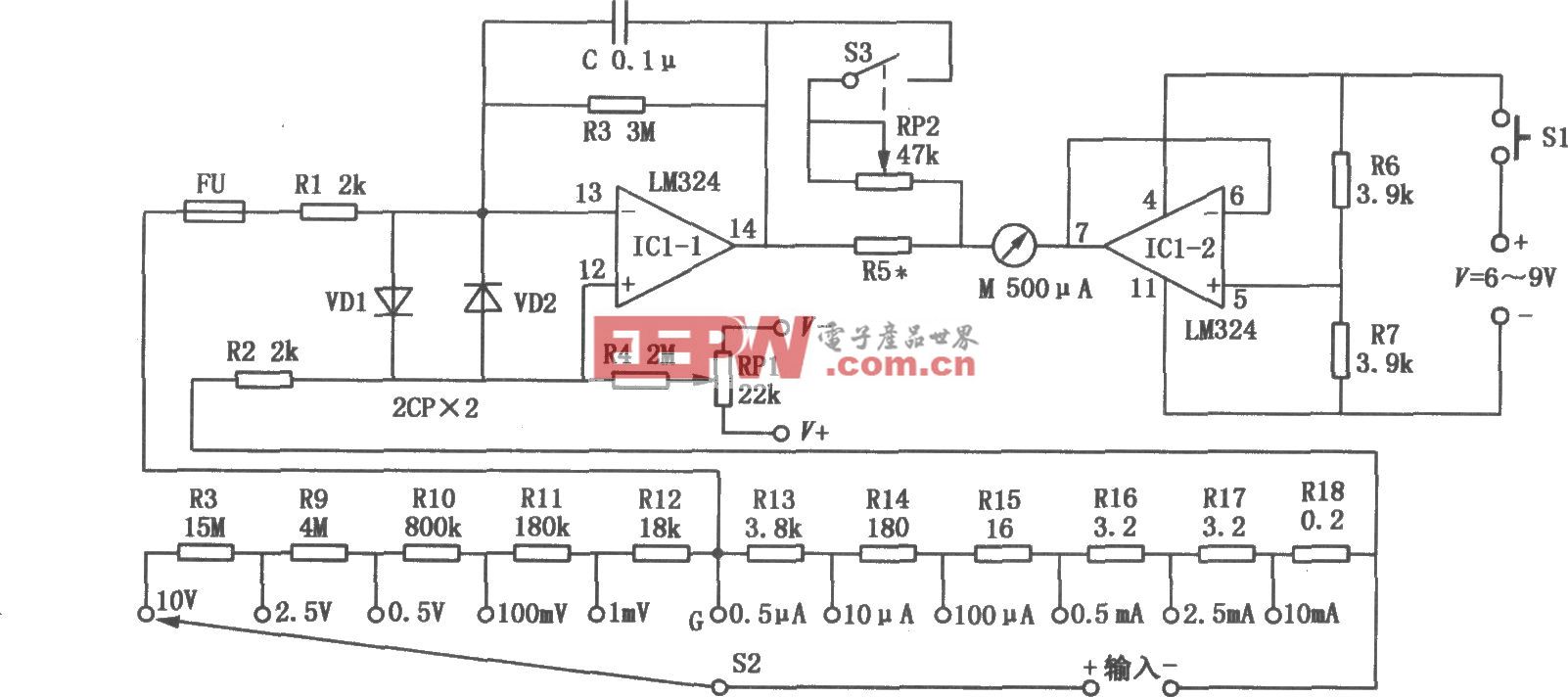

圖1顯示了使用TI SN65HVD888極性校正(POLCOR)收發器的典型電表網絡。主節點包含一個故障保護偏置電阻器網絡(RFS和RT),用于確定總線的信號極性。主節點和從節點均要求使用完整極性校正邏輯,目的是在總線閑置期間匹配總線的信號極性。這種校正邏輯由一個去抖動濾波器組成,其去抖動時間可區分相同信號極性長數據串時間和實際總線閑置時間。由于SN65HVD888的工作溫度范圍較寬,因此tFS(min)= 44 ms下限和tFS(max)= 78 ms上限之間的去抖動時間不同。

圖1 使用POLCOR收發器的典型電表總線

這就意味著,一個存在時間短至44ms的恒定總線電壓可以發起極性校正。因此,連續0位的數據串必須短于44ms,以避免引起極性校正。在網絡上電或者安裝一個新的總線節點以后通常都會要求進行極性校正,它要求總線閑置電壓的存在時間長于78ms,以確保極性校正完成。

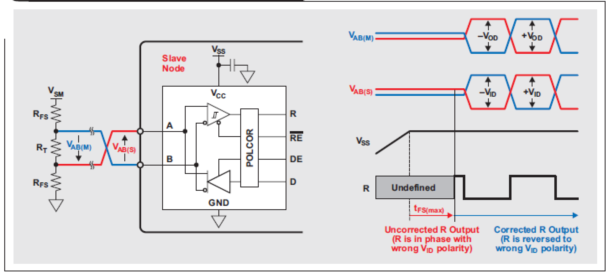

因此,時間短于44ms的恒定總線信號被視為有效數據。那些超出78ms的信號則被視為總線閑置狀態。只有小于負接收器輸入閾值(VIT_)的差分電壓才引起校正邏輯反轉信號極性。否則,收發器維持其極性狀態。圖2顯示了一個上電序列以后的極性校正例子。

在上電期間,接收器輸出(R)未定義。一旦從節點電源(VSS)穩定以后,總線必須閑置至少tFS(max),以確保極性校正完成。由于跨接故障,主節點故障保護網絡(VAB(M))的正總線電壓會以負的形式出現在收發器輸入端。因此,在tFS(max)結束以后,收發器的內部極性被切換,以反轉接收和發送數據極性。所以, 負輸入電壓(VAB(S))被轉換為正輸出電壓。

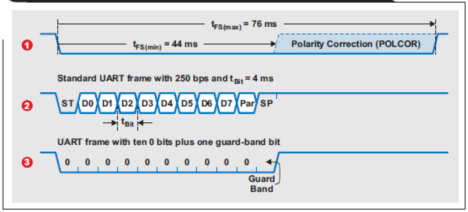

tFS(min)= 44 ms的最小去抖動時間,允許傳輸11個0位的250-bps UART框架,并且不觸發POLCOR邏輯。選擇250 bps的位速率,其低于電表使用的300 bps最小位速率。圖3顯示了UART框架的結構以及其起始、數據、極性和停止位。

圖2 上電以后的極性校正時序

圖3 標準UART框架不會觸發極性校正

使用DL/T645協議實現極性校正

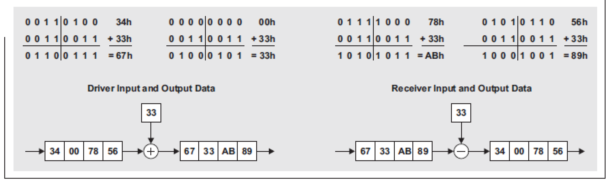

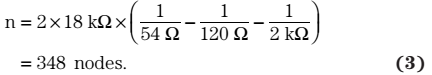

電表協議標準DL/T645說明了如何區分相同極性長數據串和總線閑置狀態。圖4表明了340078.56 W的舉例功率值如何在主從節點內得到處理。

圖4 給原始發送數據增加33h以確保相同極性短位串

DL/T645協議要求驅動從節點的測得小數值,分成多個兩位數組。每個兩位數對被轉換為16進制格式(使用“h”表示)。當這些16進制值到達驅動器輸入端時,增加33h值。然后,通過總線到主節點的驅動器輸出,發送所得到的和值。

在接收主輸入端,用接收和值減去33h,得到最初的原始發送數據。另外,數據處理再把16進制值轉換回小數格式。

圖5顯示了300bps最小速率下工作的DL/T645規范數據框架,并將其同44ms的最小去抖動時間進行比較。這里,DL/T645協議要求10個0位數據串(8個數據位加上起始位和校驗位)被轉換為最大兩個連續1或者0位的位序列。但是,由于起始位始終為0,因此在框架一開始,會出現三個連續0位的最大情況。然而,其相加時間為10ms,太短以至于無法引起意外極性校正。根據框架開始的三個0位,添加一個位作為保護帶以后,我們可以知道數據速率可安全地降低到什么程度。如果四個位分布于44ms時間窗口,則位間隔變為11ms。這帶來1/11 ms ~ 91 bps的最小數據速率。因此,我們可以肯定地說,SN65HVD888收發器支持低至100 bps的DL/T645規范數據速率。

圖5 DL/T645規范數據框架不會錯誤觸發極性校正

總線負載

為了確定主節點可以驅動的最大從節點數,需對兩種負載狀態進行評估—動態或者AC負載以及靜態或者DC負載。

AC負載

當主節點命令某個從節點發送數據并且該從節點對這種請求做出響應時,數據傳輸期間存在AC負載。在這種正常工作期間,總線上出現信號瞬態,其受到總線纜線電容、節點連接器、收發器輸入和電源的影響。為了最小化容抗對信號的影響,電表網絡工作在300 bps到20 kbps的低數據速率下。因此,下面內容僅考慮電阻性負載。

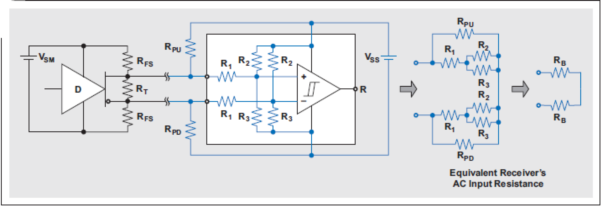

圖6顯示了主節點及其故障保護偏置網絡和遠程從接收器之間的一個簡化數據鏈。由于它們的電容較大,主節點(VSM)和從節點(VSS)的電壓電源可被看作是AC信號的短路。所以,對于主節點來說,兩個故障保護電阻器(RFS)串聯,并與端接電阻器(RT)并排放置。以類似方法連接從節點。這里,內部DC偏置電阻器(R2和R3)相互并聯,并且其組合電阻與典型高阻抗R1串聯。有時,外部上拉/下拉電阻器(分別為RPU和RPD)用于進一步對節點輸入進行偏置。這些電阻器什么作用也沒有,只會增加總線的負載,因為它們與接收器的內部電阻網絡并聯。

圖6 簡化版數據鏈

請注意,當RFS保持在1 kΩ到2 kΩ之間時,足以在主節點對低阻抗偏置網絡的整條總線進行偏置,無需再在從節點進行偏置。

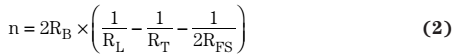

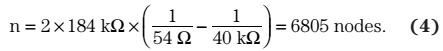

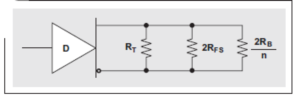

圖7顯示了所得到的等效AC電路。這里,2RB/n代表多(n)收發器的輸入電阻。由于EIA-485標準規定了最大差分驅動器負載為RL= 54 Ω,因此總線所有電阻的并聯組合必須不得超過該值。方程式1表示了這種要求:

求解n得到方程式2,得到AC負載狀態下使用的最大總線節點數:

兩種常用的網絡設計如下:

1、主節點使用一個RT=120 Ω且RFS= 1 kΩ的故障保護網絡,而每個從節點則通過RPU= RPD= 20 kΩ的外部上拉/下拉電阻器偏置,這樣RB~ 18 kΩ。在這些條件下,總線上的最大節點數便被限定在:

2、另一種情況不使用端接電阻器,而使用10kΩ的高阻抗故障保護電阻器。另外,從節點工作在沒有外部偏置的情況下(RPU= RPD= ∞)。這時,RB僅包括接收器的內部電阻(使用SN65HVD888時,其為184 kΩ每輸入)。由于這種高阻抗負載,總線節點數理論上會急劇增加至:

相比僅有40到60個節點的普通電表網絡,這兩個例子都擁有非常高的總線節點數。下一小節“DC負載”將說明,AC負載評估正在誤導我們,因為它并未考慮總線節點電源帶來的總線漏電流。

DC負載

當沒有收發器主動驅動總線時,總線閑置期間出現DC負載。在這種狀態下,主節點電源(VSM)通過附近的故障保護網絡驅動電流,從而形成正總線故障保護電壓(VFS)。這種電壓確定了所有從節點的信號極性。與主節點電源一樣,從節點電源(VSS)通過其內部電阻器網絡驅動電流。這種電流的一部分通過輸入電阻(R1)泄露進入總線。剩余電流則流經RT,然后通過反向端R1回流(圖6)。

正確接線的節點以與主節點電源相同的方向,驅動RT的電流。但是,錯誤跨接的節點會以相反方向驅動RT的電流。它會減少RT的組合電流,并影響故障保護電壓(VFS)。跨接節點達一定數量以后,VFS會變得非常小,以至于降至接收器輸入靈敏度以下,使所有總線節點進入不確定輸出狀態。為了避免出現這種狀態,必須規定主節點的故障保護網絡,以便即使所有從節點都被跨接也仍然能夠保持正VFS。

圖7 等效AC網絡

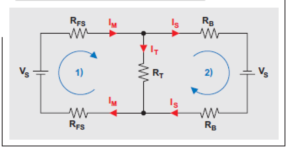

圖8僅描述了一個從節點的這種情況,目的是簡化網絡內電壓和電流關系的數學推導過程。由于VSM等于VSS,因此兩個電源可簡化為VS。

圖8 等效DC網絡

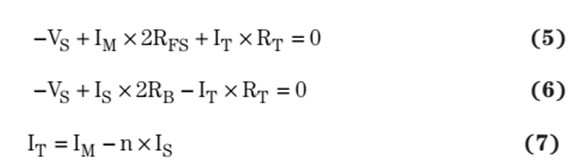

方程式5和6描述了兩個現有電壓環路,而方程式7則表示了上面相加節點的電流:

注意,方程式7中,從節點電流(IS)乘以因數n,其表示多個從節點。

求解方程式5的IM和方程式6的IS,可知道主從電流,并得到方程式8和9,其分別為:

把IM和IS的方程式插入方程式7,然后使用VFS/RT代入IT,得到:

對方程式10求解RFS,得到保持VFS為正所必需的故障保護電阻器值:

對于沒有端接電阻器(RT= ∞)的應用來說,方程式11可簡化為:

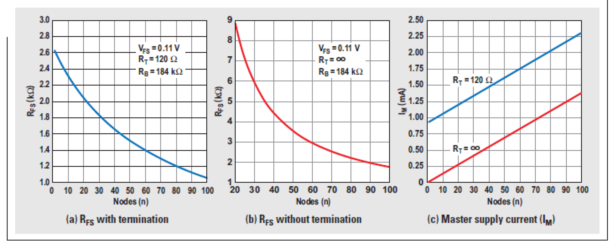

圖9顯示了RFS的值和主節點電源電流(IM)與總線節點數目的關系。使用方程式11得到圖9a,其假設端接電阻器為120 Ω。使用方程式12得到圖9b,其假設沒有端接電阻器。兩幅圖的故障保護電壓均為110 mV。

圖9 有無端接的故障保護電阻(RFS)的效果

圖9c顯示了兩種情況的主節點電源電流(IM)。盡管低阻抗負載為120 Ω,但使用端接的故障保護網絡電流IM僅為1mA,大于無端接電阻器的網絡電流IM。

結論

SN65HVD888 POLCOR通過去抖動濾波,提供跨接總線線纜的極性校正。濾波器的最小去抖動時間(tFS(min))決定了相同極性最大連續位時間,而其最大去抖動時間(tFS(max))則決定了一次完整信號極性校正的最小總線閑置時間。

僅在上電序列以后,SN65HVD888才要求進行極性校正。一旦完成,極性狀態便存儲于收發器內,并一致應用于接收和發送數據。在發送和接收模式之間切換收發器,不會改變極性狀態。

這種收發器支持300 bps以下的DL/T645數據速率。推薦故障保護偏置網絡使用一個120Ω端接電阻器和兩個1.1kΩ故障保護偏置電阻器。

參考文獻

1、《帶IEC-ESD保護的總線極性校正RS-485收發器》,見于《SN65HVD888產品說明書》,網址:www.ti.com/sllseh3-aaj

2、《DL/T645-1997多功能瓦時電表通信協議》,中華人民共和國電力部。

3、《TIA/EIA-485(RS-485)接口電路》,見于《應用報告》,網址:www.ti.com/slla036-aaj

4、《RS-422和RS-485標準概覽與系統配置》,見于《應用報告》,網址:www.ti.com/slla070-aaj

5、《平衡數字多點系統中TIA/EIA-485-A生成器和接收器的電特性》,2003年,電信行業協會,網址:www.tiaonline.org

6、《TIA/EIA-TSB 89:TIA/EIA-485-A應用指南》,2006年1月1日,電信行業協會,網址:www.techstreet.com/products/1525598

7、《ISO/IEC 8482:1993年信息技術(系統間遠程通信與信息交換)雙絞線多點互連》,1993年,國際標準組織,網址:www.iso.org

相關網站

訪問入口:

www.ti.com/interface-aaj

www.ti.com/sn65hvd82-aaj

www.ti.com/sn65hvd888-aaj

《模擬應用期刊》訂閱:

www.ti.com/subscribe-aaj

評論