高速數字電路封裝電源完整性分析

接著,我們固定Pkg厚度為0.15mm,分別改變PCB厚度為0.15mm、0.4mm、0.8mm、1.6mm,PCB厚度對S參數的影響結果如圖13所示,可以看到PCB電源層厚度對整體趨勢影響并不大,只有低頻部分少有差異,厚度增加第一個零點小高頻移動,高頻部分只稍有差異。

本文引用地址:http://cqxgywz.com/article/201610/311828.htm

圖13 不同PCB電源層厚度對|S21|的影響

電容擺放距離的影響

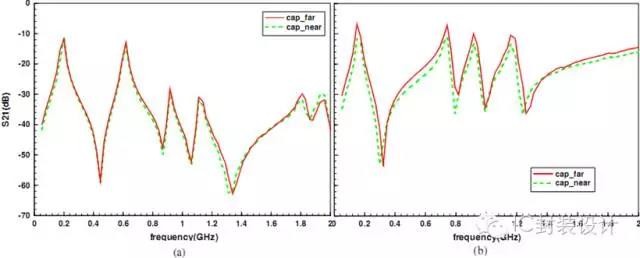

我們知道去耦電容的位置距離噪聲源越近越好,因為能減少電容到噪聲源之間的電感值,讓電容更快的吸收突波,降低噪聲,達到穩定電壓的作用。同樣降低電源層厚度能減小電源平面寄生電感,也能起到相同作用。在模擬上我們改變電容在封裝上和測試點之間的距離,分別為1.7cm和0.2cm,Pkg和PCB電源層厚度分兩種情況,第一種Pkg 0.15mm和PCB 0.7mm,第二種情況,Pkg1.6mm和PCB 0.7mm,電容100nF、ESR 0.04ohm、ESL 0.63nH。

圖14 電容與測試點的距離

圖15 不同電容與測試點的距離|S21|模擬結果

由模擬結果得知,當因為封裝結構或繞線問題,不能把電容放置在噪聲源附近是,我們可以藉由減低Pkg電源層厚度,減少噪聲的影響。

四、結論

最后,我們對高速數字電路如何中抑制噪聲做一總結。首先,去耦電容的理想位置是放置在Pkg上;ESR增大雖能把極點鏟平,但也會導致共振頻率深度變淺,電容充放電時間增大,會失去降低電源平面阻抗的功能;電容ESL增大會加快共振點后阻抗上升速度,所以ESL越低越好;電容數量越多越好,電容墻可以提高隔離效果;電容容值的選擇,需要根據噪聲頻段來選擇,盡量不要多容值混用,雖然這樣能增加噪聲抑制的頻寬,但也會增加共振點數量,如果噪聲剛好落在共振點上,疊加的效果可能會更嚴重;PCB電源平面厚度對Pkg上的S參數幾乎沒有影響,但在低頻,Pkg上板層厚度卻會影響PCB耦合上來的噪聲大小,Pkg板層越薄耦合上來的噪聲越小;高頻部分,主要受封裝影響,Pkg板層越薄,|S21|值越小。

評論