51手記之C8051F

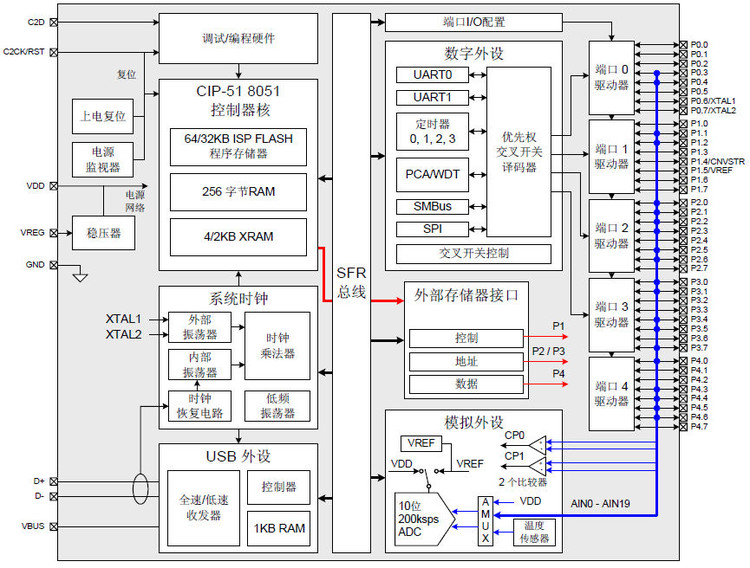

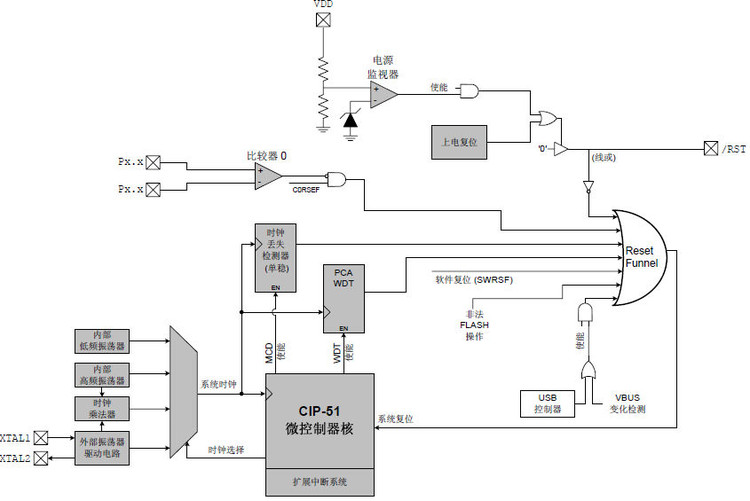

CIP-51共有111條指令。下表列出了指令條數與執行時所需的系統時鐘周期數的關系。

器件內部包含一個穩壓器(REG0)。當被使能時,REG0輸出連到VDD引腳,并可為外部器件提供電源。REG0可以被軟件使能/禁止。

可在工業溫度范圍(-45℃到+85℃)內用2.7V-5.25V的電壓工作。電源電壓大于3.6V時,必須使用內部穩壓器。

包含C2調試接口,支持FLASH編程和使用安裝在最終應用系統中的器件進行在系統調試。1.基本特性

時鐘源:有1個可編程內部高頻振蕩器、1個可編程內部低頻振蕩器、1個外部振蕩器驅動電路和1個4倍時鐘乘法器。

高速內部振蕩器在出廠時已經被校準為12MHz±1.5%。時鐘恢復電路允許內部振蕩器與4倍時鐘乘法器配合,提供全速方式USB時鐘源。內部振蕩器還被用作低速方式下的USB時鐘源。器件內集成了外部振蕩器驅動電路,允許使用晶體、陶瓷諧振器、電容、RC或外部CMOS時鐘源產生系統時鐘。

系統時鐘可以被配置為使用內部振蕩器、外部振蕩器或時鐘乘法器輸出二分頻。如果需要,可以在CPU運行時切換系統時鐘振蕩源。低頻內部振蕩器或外部振蕩器在低功耗系統中是非常有用的,它允許MCU從一個低頻率(節電)的時鐘源運行,當需要時再周期性地切換到高速時鐘源。

外部晶體使用步驟:a.使能外部振蕩器;b.等待至少1ms;c.查詢XTLVLD =>‘1’;d.將系統時鐘切換到外部振蕩器。

4倍時鐘乘法器配置:a.通過向寄存器CLKMUL寫0x00來復位時鐘乘法器;b.用MULSEL位選擇時鐘乘法器的輸入;c.用MULEN位使能時鐘乘法器(CLKMUL | = 0x80);d.延時大于5 μs;e.用MULINIT位初始化時鐘乘法器(CLKMUL | = 0xC0);f.查詢等待MULRDY =>‘1’。

當使用外部振蕩器作為4倍時鐘乘法器的輸入時,外部振蕩源必須在乘法器初始化之前被使能并穩定運行。

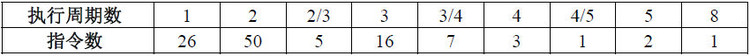

有9個復位源:上電復位電路(POR)、片內VDD監視器(當電源電壓低于VRST時強制復位)、USB控制器(USB總線復位或VBUS狀態變化)、看門狗定時器、時鐘丟失檢測器、由比較器0提供的電壓檢測器、軟件強制復位、外部復位輸入引腳和FLASH讀/寫錯誤保護電路復位。除了POR、復位輸入引腳及FLASH操作錯誤這三個復位源之外,其他復位源都可以被軟件禁止。在一次上電復位之后的MCU初始化期間,WDT可以被永久性使能。

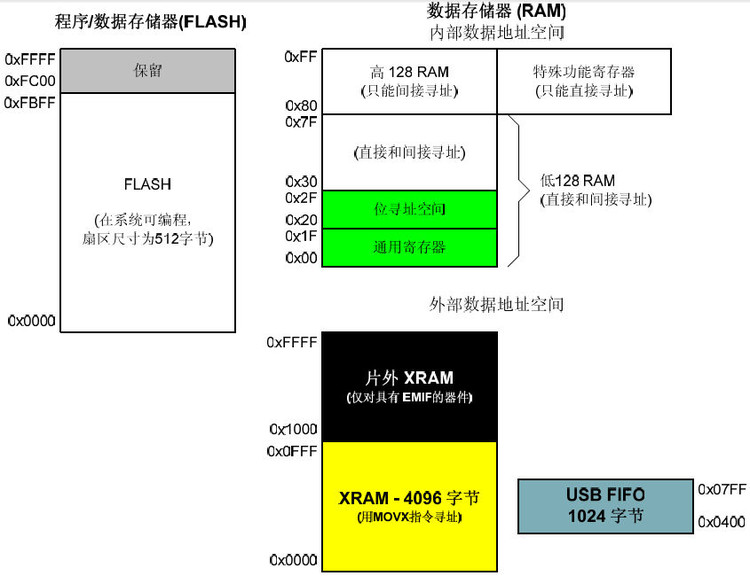

2.存儲器

1)程序存儲器

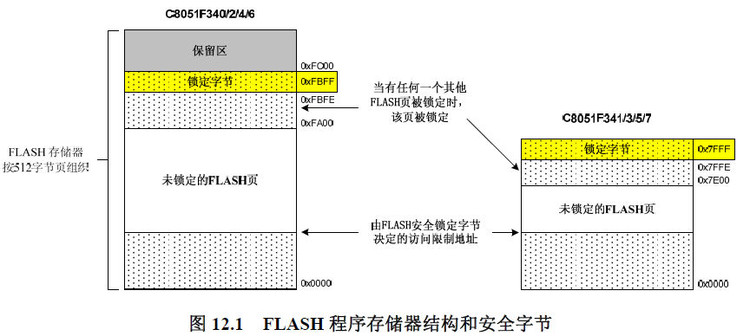

內部有可再編程的FLASH存儲器,用于程序代碼和非易失性數據存儲。可以通過C2接口或由軟件使用MOVX指令對FLASH存儲器進行在系統編程,每次一個字節。可在系統編程,扇區大小為512字節。

64KB的片內FLASH存儲器可用作程序存儲器或可編程數據存儲器,實際使用過程中需注意,程序默認從低地址開始存放,如需使用該空間存放數據,需避開程序代碼區。只有未鎖定的FLASH頁可使用。

2)數據存儲器

片上256字節RAM+4KB的XRAM,1KB的USB FIFO也可以被映射到外部數據存儲器空間,作為通用數據存儲器使用。有用于訪問片外存儲器和存儲器映射器件的外部存儲器接口EMIF。

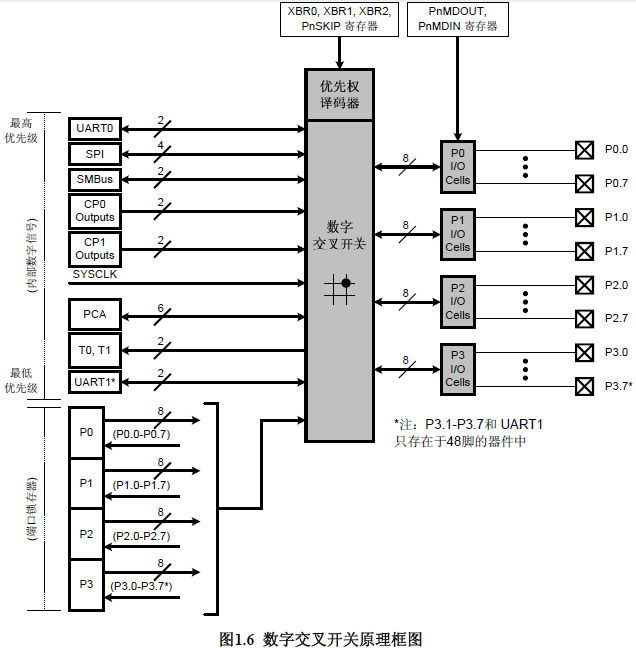

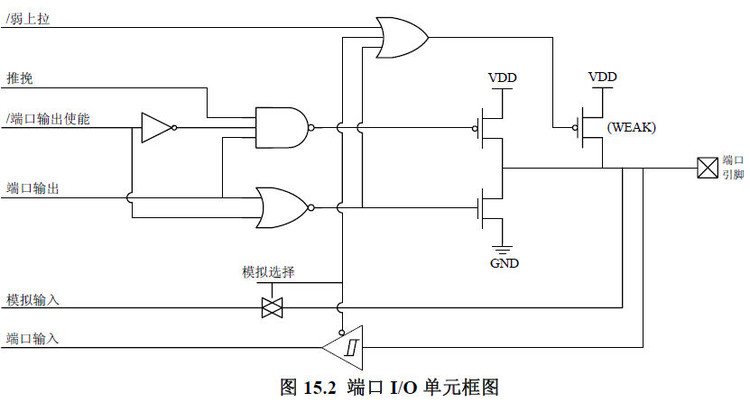

有40/25個I/O口,均耐5V電壓,大灌電流。每個端口引腳都可以被配置為模擬輸入或數字I/O引腳,被選擇為數字I/O的引腳還可以被配置為推挽或漏極開路輸出。

數字交叉開關允許將內部數字系統資源映射到端口I/O引腳,交叉開關根據優先權譯碼表為所選擇的內部數字資源分配I/O引腳。寄存器XBR0、XBR1和XBR2用于選擇內部數字功能。。PnSKIP寄存器允許軟件跳過那些被用作模擬輸入、特定功能或GPIO的引腳。

a.用端口輸入方式寄存器(PnMDIN)選擇所有端口引腳的輸入方式(模擬或數字)。

b.用端口輸出方式寄存器(PnMDOUT)選擇所有端口引腳的輸出方式(漏極開路或推挽)。

c.用端口跳過寄存器(PnSKIP)選擇應被交叉開關跳過的那些引腳。

d.將引腳分配給要使用的外設(XBR0、XBR1、XBR2)。

e.使能交叉開關(XBARE = 1)。

所有端口引腳都必須被配置為模擬或數字輸入。被用作比較器或ADC輸入的任何引腳都應被配置為模擬輸入。為使端口P0、P1、P2和P3工作在標準端口I/O輸出方式,交叉開關必須被使能。當交叉開關被禁止時,端口輸出驅動器被禁止。端口4總是作為標準GPIO使用。

所有端口引腳都必須被配置為模擬或數字輸入。被用作比較器或ADC輸入的任何引腳都應被配置為模擬輸入。為使端口P0、P1、P2和P3工作在標準端口I/O輸出方式,交叉開關必須被使能。當交叉開關被禁止時,端口輸出驅動器被禁止。端口4總是作為標準GPIO使用。

未被交叉開關分配的端口引腳和未被模擬外設使用的端口引腳都可以作為通用I/O。通過對應的端口數據寄存器訪問端口P3-0,這些寄存器既可以按位尋址也可以按字節尋址。端口P4(僅C8051F340/1/4/5)使用的SFR只能按字節尋址。

4.中斷系統

4.中斷系統

支持16個中斷源,每個中斷源有兩個優先級。中斷源在片內外設與外部輸入引腳之間的分配隨器件的不同而變化。

兩個外部中斷源/INT0和/INT1可被配置為低電平有效或高電平有效,邊沿觸發或電平觸發。IT01CF寄存器中的IN0PL(/INT0極性)和IN1PL(/INT1極性)位用于選擇高電平有效還是低電平有效;TCON中的IT0和IT1用于選擇電平或邊沿觸發。

在FLASH寫/擦除操作期間和USB FIFO MOVX訪問期間,CPU暫停執行指令。對于在CPU暫停執行指令期間發生的中斷,中斷服務響應時間將延長。

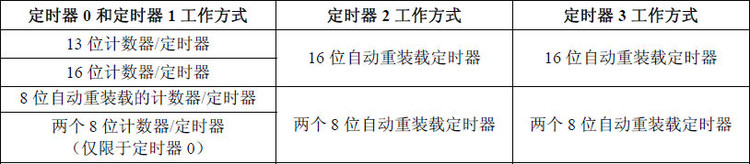

5.定時器

內部有4個16位計數器/定時器:其中兩個與標準8051中的計數器/定時器兼容,另外兩個是16位自動重裝載定時器,可用于ADC、SMBus、USB(幀測量)、低頻振蕩器(周期測量)或作為通用定時器使用。這些定時器可以用于測量時間間隔,對外部事件計數或產生周期性的中斷請求。

定時器0和定時器1有5個可選擇的時鐘源,定時器2和定時器3可以使用系統時鐘、系統時鐘/12或外部振蕩器時鐘/8作為時鐘源。

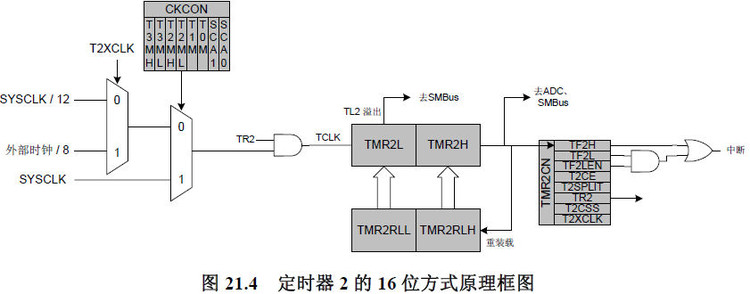

定時器2,3可以工作在16位自動重裝載方式、8位自動重裝載方式(兩個8位定時器)、USB幀起始(SOF)捕捉方式或低頻振蕩器(LFO)下降沿捕捉方式。當T2SPLIT =‘0’且T2SOF =‘0’時,定時器2工作在自動重裝載的16位定時器方式:

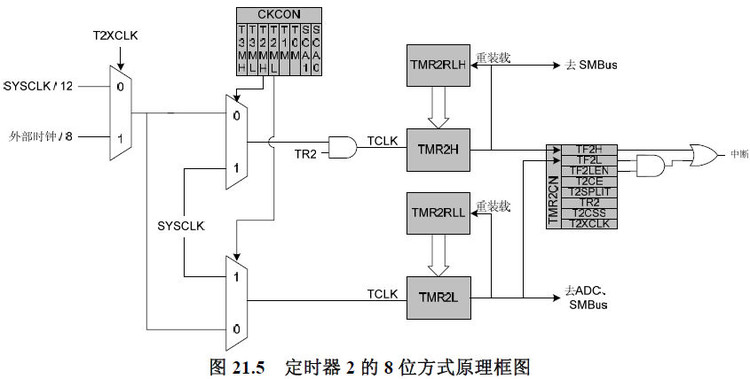

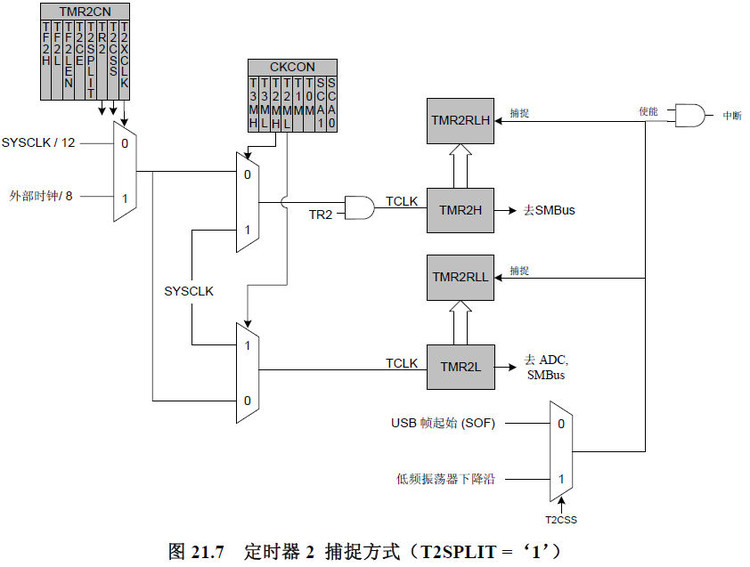

當T2SPLIT =‘1’且T2SOF =‘0’時,定時器2工作雙8位定時器方式。兩個8位定時器TMR2H和TMR2L都工作在自動重裝載方式。TMR2RLL保持TMR2L的重載值,而TMR2RLH保持TMR2H的重載值。TMR2CN中的TR2是TMR2H的運行控制位。當定時器2被配置為8位方式時,TMR2L總是處于運行狀態。

TF2H和TF2L標志不能被硬件自動清除,必須通過軟件清除。

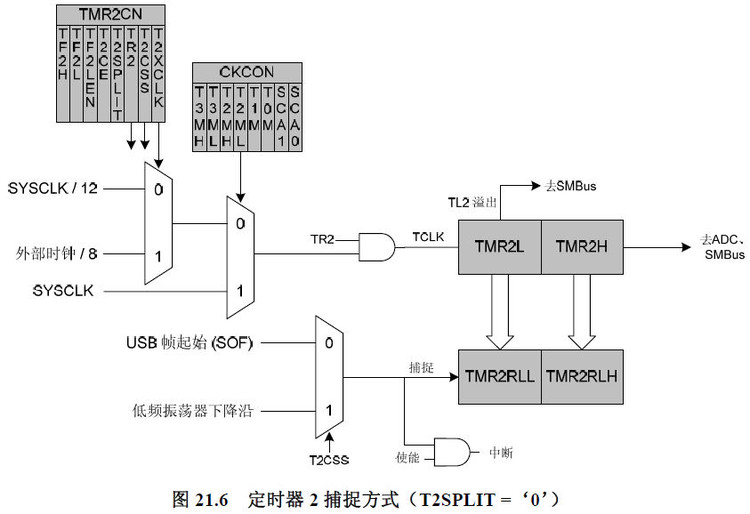

當T2CE =‘1’時,定時器2工作在兩種特殊捕捉方式之一。捕捉事件可以是USB幀起始(SOF)捕捉或低頻振蕩器(LFO)下降沿捕捉,用T2CSS位選擇。

6.串行口

2個全雙工串行口,UART0有2種工作方式:提供標準8051串行口的方式1和方式3。

UART0具有增強的波特率發生器電路,有多個時鐘源可用于產生標準波特率,接收數據緩沖機制允許UART0在軟件尚未讀取前一個數據字節的情況下開始接收第二個輸入數據字節。UART0波特率由定時器1工作在8位自動重裝載方式產生。發送(TX)時鐘由TL1產生;接收(RX)時鐘由TL1的拷貝寄存器(RX定時器)產生,TX和RX定時器的溢出信號經過二分頻后用于產生TX和RX波特率。定時器1的時鐘可以在6個時鐘源中選擇:SYSCLK、SYSCLK/4、SYSCLK/12、SYSCLK/48、外部振蕩器時鐘/8和外部輸入T1。

UART0的波特率=T1clk/(256-T1H)/2

多機通訊:所有從機的RX和TX分別并接到主機的TX和RX上,從機的MCE0位(SCON.5)被置‘1’,只有當UART接收到的第九位為邏輯‘1’ (RB80=1)并收到有效的停止位后UART才會產生中斷。當主機要發送數據給一個或多個從機時,它先發送一個用于選擇目標的地址字節(地址字節所有從機都接收,對應地址的從機收到該地址后,清MCE0,以便能接收數據)。地址字節與數據字節的區別是:地址字節的第9位為邏輯‘1’;數據字節的第9位總是設置為邏輯‘0’。

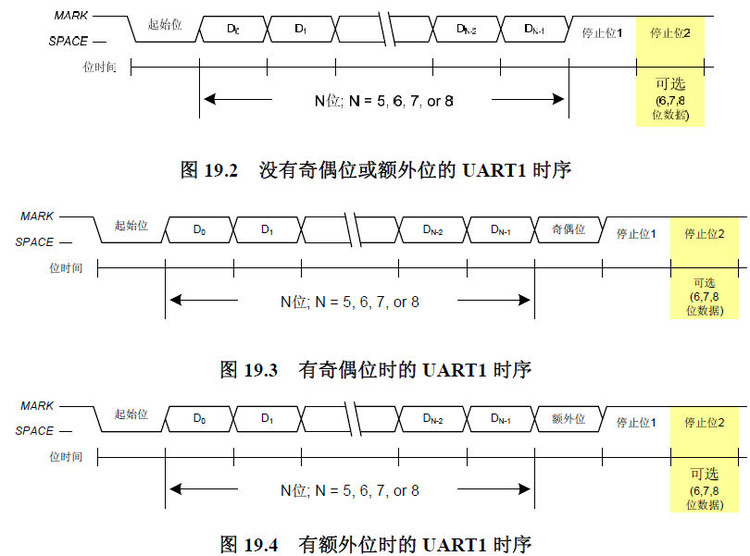

UART1包含一個由16位定時器和可編程預分頻器構成的專用波特率發生器,能產生很寬范圍的波特率。UART1數據傳輸以起始位(邏輯低電平)開始,其后是數據位(LSB在先),數據位之后是奇偶位或額外位(如果選擇),最后是一個或兩個停止位(邏輯高電平)。數據長度在5 ~ 8位之間。UART1的工作方式設置與標準51不同。多機通訊時,額外位與UART0的第9位功能類似。

UART1的波特率=Fosc/(65536-(SBRLH1:SBRLL1))/2/預分頻值

7.增強型串行外設接口SPI0

增強型串行外設接口(SPI0)提供訪問一個全雙工同步串行總線的能力。SPI0可以作為主器件或從器件工作,可以使用3線或4線方式,并可在同一總線上支持多個主器件和從器件。

8.SMBus

SMBus I/O接口是一個雙線的雙向串行總線。與I2C串行總線兼容。在作為主或從器件時,數據傳輸的最大速率可達系統時鐘頻率的十分之一(這可能比SMBus的規定速度要快,取決于所使用的系統時鐘)。可以采用延長低電平時間的方法協調同一總線上不同速度的器件。。SMBus提供了SDA(串行數據)控制、SCL(串行時鐘)產生和同步、仲裁邏輯以及起始/停止的控制和產生電路。

SCL(串行時鐘)和SDA(串行數據)線是雙向的,必須通過一個上拉電阻或等效電路將它們連到電源電壓。連接在總線上的每個器件的SCL和SDA都必須是漏極開路或集電極開路的,因此當總線空閑時,這兩條線都被拉到高電平。總線上的最大器件數只受規定的上升和下降時間的限制,上升和下降時間分別不能超過300ns和1000ns。

所有的數據傳輸都由主器件啟動,可以尋址一個或多個目標從器件。主器件產生一個起始條件,然后發送地址和方向位。

一個主器件只能在總線空閑時啟動一次傳輸。在一個停止條件之后或SCL和SDA保持高電平已經超過了指定時間,則總線是空閑的。兩個或多個主器件可能在同一時刻啟動數據傳輸,所以使用仲裁機制迫使一個主器件放棄總線。試圖發送高電平的主器件將檢測到SDA上的低電平而退出競爭。贏得總線的器件繼續其數據傳輸過程,而未贏得總線的器件成為從器件并在后續的傳輸中接收數據(如果被尋址)。

每次數據字節或從地址傳輸都產生SMBus中斷。發送數據時在ACK周期后產生中斷,使軟件能讀取接收到的ACK值;接收數據時在ACK周期之前產生中斷,使軟件能確定要發出的ACK值。

SMBus接口可以被配置為工作在主方式和/或從方式。在任一時刻,它將工作在下述4種方式之一:主發送器、主接收器、從發送器或從接收器。

9.可編程計數器陣列(PCA0)

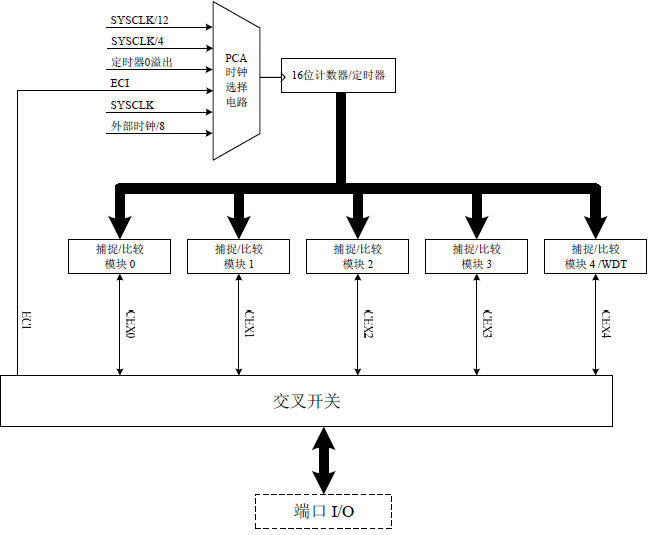

提供增強的定時器功能,與標準8051的計數器/定時器相比,它需要較少的CPU干預。PCA由一個專用的16位計數器/定時器和5個16位捕捉/比較模塊組成。每個捕捉/比較模塊有其自己的I/O線(CEXn),這些I/O線在被允許時通過交叉開關連到端口I/O。

定時器的時基信號可以在六個時鐘源中選擇:系統時鐘、系統時鐘/4、系統時鐘/12、外部振蕩器時鐘/8、定時器0溢出或ECI輸入引腳上的外部時鐘信號。

PCA的模塊4可被用作看門狗定時器(WDT),在系統復位后即被使能為該方式。在看門狗方式被使能時,對某些寄存器的訪問受到限制

1)PCA計數器/定時器

16位的PCA計數器/定時器由兩個8位的SFR組成:PCA0L和PCA0H。在讀PCA0L時,“瞬象寄存器”自動鎖存PCA0H的值,隨后讀PCA0H時將訪問這個“瞬象寄存器”;先讀PCA0L寄存器可以保證正確讀取整個16位PCA計數器的值。

當計數器/定時器溢出時(從0xFFFF到0x0000),PCA0MD中的計數器溢出標志(CF)被置為邏輯‘1’并產生一個中斷請求

2)捕捉/比較模塊

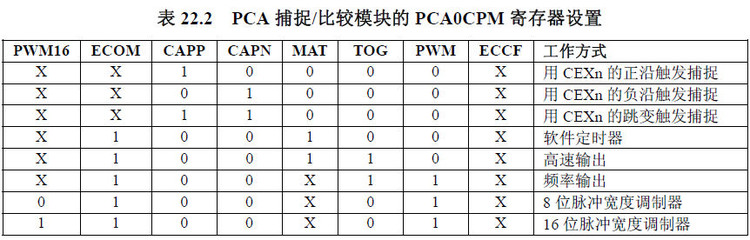

每個模塊都可被配置為獨立工作,有六種工作方式:邊沿觸發捕捉、軟件定時器、高速輸出、頻率輸出、8位脈寬調制器和16位脈寬調制器。

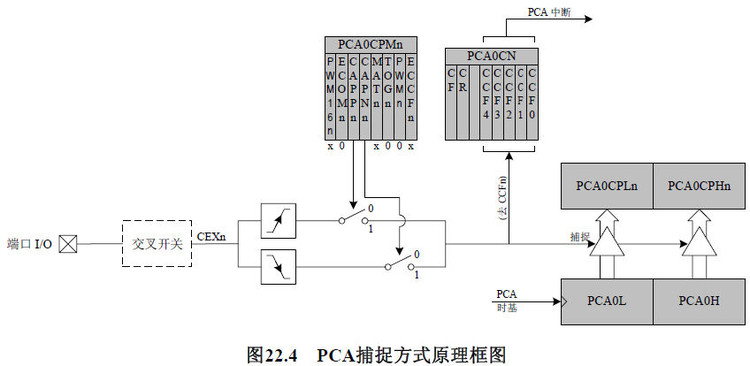

a.邊沿觸發的捕捉方式

CEXn輸入信號必須在高電平或低電平期間至少保持兩個系統時鐘周期,以保證能夠被硬件識別。

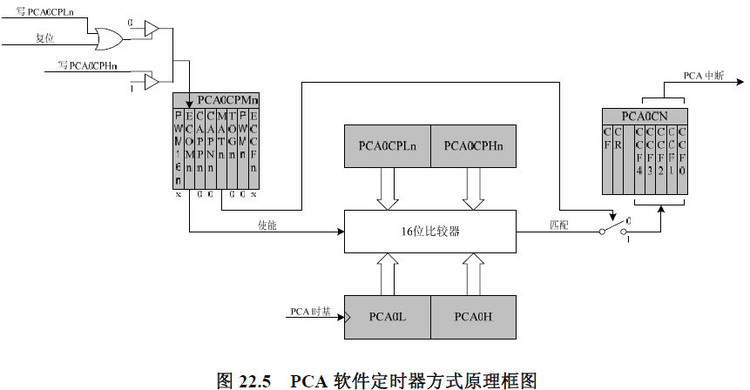

b.軟件定時器方式

在該方式,PCA將計數器/定時器的計數值與模塊的16位捕捉/比較寄存器(PCA0CPHn和PCA0CPLn)進行比較。當發生匹配時,PCA0CN中的捕捉/比較標志(CCFn)被置為邏輯‘1’并產生一個中斷請求;當向PCA0的捕捉/比較寄存器寫入一個16位數值時,應先寫低字節。

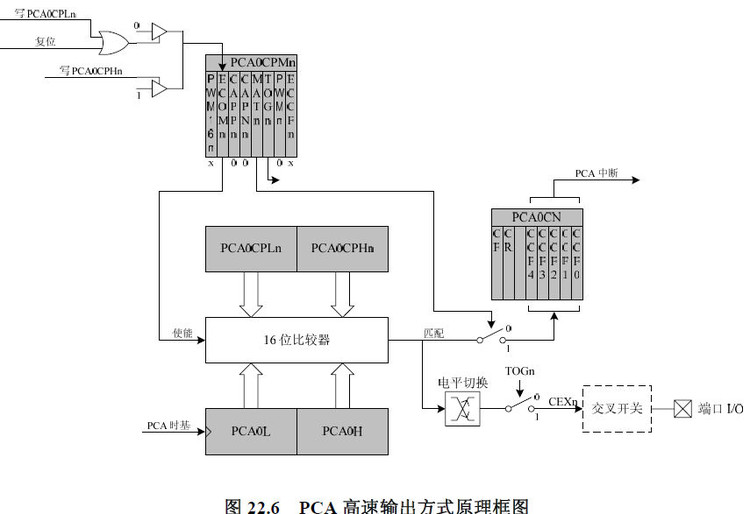

c.高速輸出方式

每當PCA計數器與模塊的16位捕捉/比較寄存器(PCA0CPHn和PCA0CPLn)發生匹配時,模塊的CEXn引腳上的邏輯電平將發生變化。當向PCA0的捕捉/比較寄存器寫入一個16位數值時,應先寫低字節。

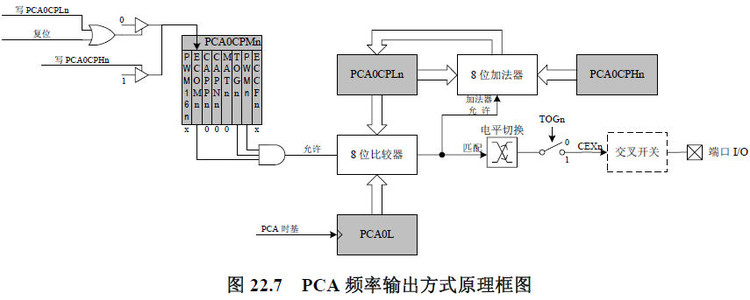

d.頻率輸出方式

可在模塊的CEXn引腳產生可編程頻率的方波。。捕捉/比較模塊的低字節與PCA0計數器的低字節比較;兩者匹配時,CEXn的電平發生改變, 方波頻率=Fpca/(2*PCA0CPHn),PCA0CPHn中的值為0x00時,相當于256。

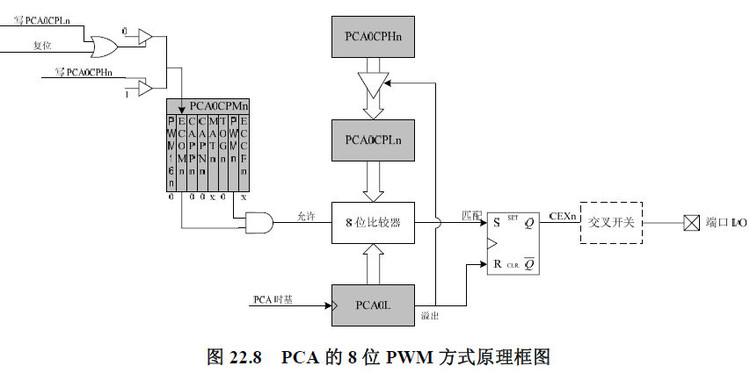

e.8位脈寬調制器方式

PWM輸出的頻率取決于PCA計數器/定時器的時基。使用模塊的捕捉/比較寄存器PCA0CPLn改變PWM輸出信號的占空比。當PCA計數器/定時器的低字節(PCA0L)與PCA0CPLn中的值相等時,CEXn引腳上的輸出被置‘1’;當PCA0L中的計數值溢出時,CEXn輸出被復位

占空比=(256-PCA0CPHn)/256

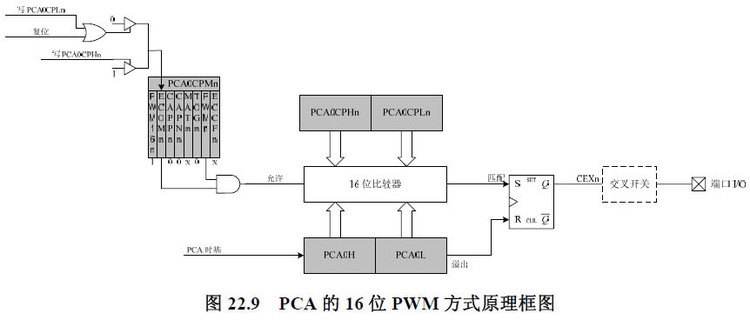

f.16位脈寬調制器方式

當PCA計數器與模塊的值匹配時,CEXn的輸出被置為高電平;當計數器溢出時,CEXn輸出被置為低電平。為了輸出一個占空比可變的波形,新值的寫入應與PCA的CCFn匹配中斷同步。

占空比=(65536-PCA0CPn)/65536

3)看門狗定時器

通過PCA的模塊4可以實現可編程看門狗定時器(WDT)功能。模塊4高字節與PCA計數器的高字節比較;模塊4低字節保持執行WDT更新時要使用的偏移值。在系統復位后看門狗被使能。在看門狗被使能時,對某些PCA寄存器的寫操作受到限制。

如果在WDT被使能時PCA0CPH4和PCA0H發生匹配,則系統將被復位。為了防止WDT復位,需要通過寫PCA0CPH4來更新WDT。在寫PCA0CPH4時,PCA0H的值加上PCA0CPL4中保存的偏移值后被裝入到PCA0CPH4. 當WDT被使能時:

a.PCA計數器被強制運行。

a.PCA計數器被強制運行。

b.不允許寫PCA0L和PCA0H。

c.PCA時鐘源選擇位(CPS2-CPS0)被凍結。

d.PCA等待控制位(CIDL)被凍結。

e.模塊4被強制進入看門狗定時器方式。

f.對模塊4方式寄存器(PCA0CPM4)的寫操作被禁止。

看門狗定時器偏移值(PCA時鐘數)=(256*PCA0CPL4)+(256-PCA0L)

配置WDT的步驟如下:

a.通過向WDTE位寫‘0’來禁止WDT。

b.選擇PCA時鐘源(用CPS2-0位)。

c.向PCA0CPL4裝入所希望的WDT更新偏移值。

d.配置PCA的空閑方式位(如果希望在CPU處于空閑方式時WDT停止工作,則應將CIDL位置‘1’)。

e.通過向WDTE位寫‘1’來使能WDT。

f.(選項)通過將WDLCK位置‘1’來鎖定WDT(防止在下一次系統復位前禁止WDT)。

WDT在任何一次系統復位之后都被設置為使能狀態。PCA0計數器的缺省時鐘為系統時鐘的十二分頻(SYSCLK/12)。當WDTE位被置1時,不能改變PCA0MD寄存器的值。若要改變PCA0MD的內容,必須先禁止看門狗定時器。

評論