ARM處理器架構處理器的工作狀態

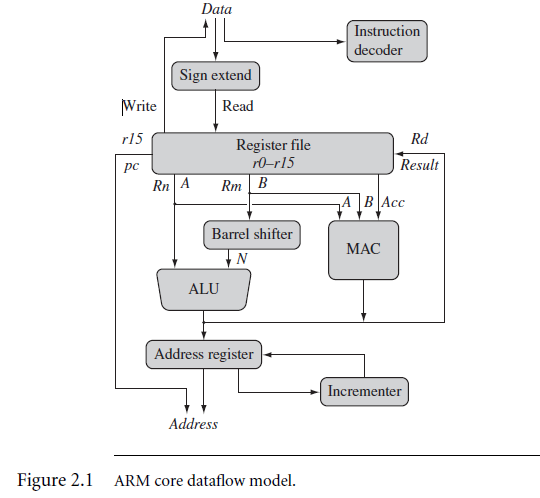

從編程人員的視角來看,arm核是由數據總線連接的功能單元組成,如下圖所示:

本文引用地址:http://cqxgywz.com/article/201611/317948.htm

數據通過數據總線流向處理器核心,這里的數據可以是將要執行的指令,也可以是數據項.上面的圖是Von Neumann體系的arm核,數據項和指令共用同一總線.而哈佛結構體系的arm核就會用兩個不同的總線.就像所有的RISC處理器,arm采用load-store體系結構.也就是說它含有兩條不同的指令類型來出入處理器.load指令將數據從內存拷貝到寄存器,store指令是將數據從寄存器拷貝到內存.沒有直接操作內存中數據的數據處理指令.數據的處理離不開寄存器.

ARM指令一般有兩個源寄存器,Rn和Rm,和一個目的寄存器,Rd. ARM的一個重要特性是Rm可以在送入ALU之前被桶型移位器做預處理,這樣就會有很多形式的表達式和尋址方式. 后面再寫博客記錄一下arm中的指令集。

下面介紹ARM處理器的幾個關鍵分量:寄存器,當前程序狀態寄存器和流水線

一、寄存器。

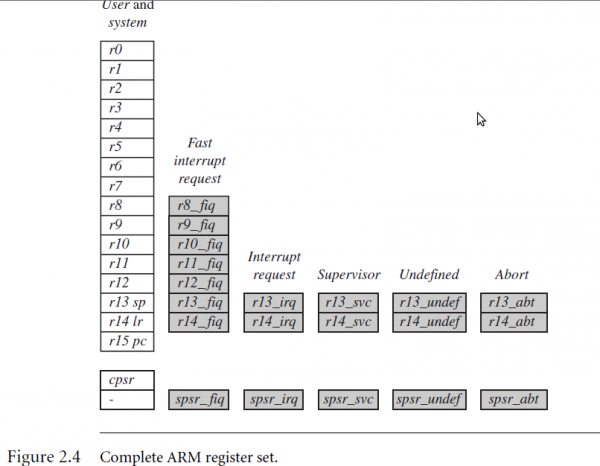

arm核一共有37個寄存器,有7種工作模式。其中在任一種工作模式下,可見的寄存器通常有18個(在user/system模式下可見的是17個)。另外,某幾個寄存器(sp、lr、spsr)在不同的模式下對應的是不同的寄存器,所以總數加起來共有37個。所有的寄存器都是32bit大小.

18個活動的寄存器包括:16個數據寄存器和2個程序狀態寄存器.

(1)數據寄存器由r0--r15表示. 其中r0-r12是通用寄存器,r13-r15是三個特殊的寄存器。

r13通常用作棧指針(sp),存儲當前處理器工作模式下的棧頂;

r14被稱作鏈接寄存器(lr),當發生函數調用時存放當前的pc指針,作為子程序的返回地址;

r15被稱作程序計數器(pc),保存被處理器預取的下一條指令的地址.

這三個寄存器,在寫匯編語句的時候都不用r13這種來表示,都是用sp、lr、pc來表示的。

(2)兩個程序狀態寄存器:cpsr和spsr. 處理器的當前工作模式決定了哪些寄存器是可見的.

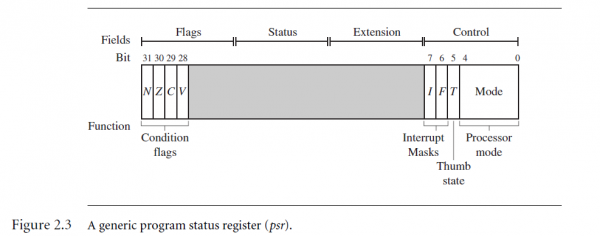

cpsr:當前程序狀態寄存器。ARM核使用cpsr來顯示和控制內部的操作.通用程序狀態寄存器的內部如下:

cpsr分為四個域,每個域有8位的寬度:flags,status,extension和control.control域包含處理器模式和狀態以及中斷屏蔽位.flags域包含condition flags.處理器模式決定了當前哪些寄存器是可用的以及cpsr本身的訪問權限.

當發生異常時,arm會自動將cpsr保存到spsr寄存器中。

二、 處理器模式

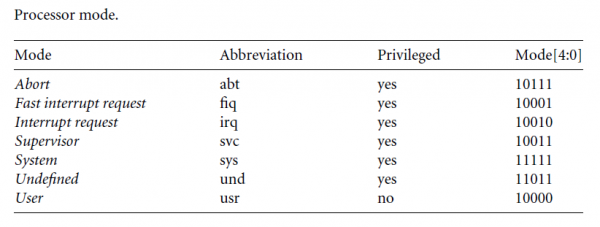

處理器模式分為特權模式和非特權模式:特權模式對cpsr有完全的讀寫控制.而非特權模式只能讀cpsr的control域但是仍可以讀寫condition flags.一共有7種處理器模式:六種特權模式(abort,fiq,irq,svc,system和undefined)和一種非特權模式(user).

abort:當試圖訪問內存失敗時處理器會進入abort模式;

fiq和irq對應ARM處理器的兩種中斷級別, irq是普通的中斷模式,fiq是快速中斷模式。

svc是系統reset后進入的默認模式,也是os kernel工作的模式;

system模式是user模式的特殊版本,它有對cpsr的讀寫控制.

undefined模式在處理器遇到未定以的指令或者不支持的操作時使用.

user模式在應用程序下使用.

在不同的模式下,有不同的Banked registers。所謂的banked register 就是說 這個寄存器是該模式所獨有的,不與其他模式共享。

除了user模式,其它模式都可以通過直接寫cpsr的模式位來改變處理器模式.當然,在異常或者中斷到來時,硬件會自動切換模式.

下列異常和中斷會引起模式切換:reset,irq,fiq,swi,data abort,prefetch abort和undefined instruction.

三、cpsr寄存器。

下面接著講cpsr寄存器。處理器模式對應的cpsr寄存器:

需要注意的是:通過直接寫cpsr來改變模式的方法不會將cpsr拷貝到spsr.只有在異常或中斷發生時cpsr的值才會保存到spsr。

當ARM核上電時,處于svc特權模式.從特權模式開始是有用的:初始化代碼完全控制cpsr來建立其他模式的堆棧.

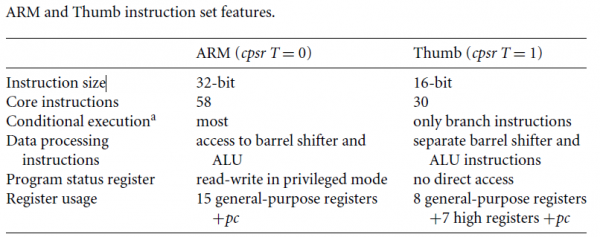

cpsr中的bit T是表明指令簇用的是ARM指令集還是thumb指令集.T為1表示thumb指令集,T為0表示ARM指令集.

ARM指令集和thumb指令集的特性:

中斷屏蔽位:中斷屏蔽位用來屏蔽處理器的特殊中斷請求.在ARM核中有兩種級別的中斷請求:irq和fiq.

cpsr中的中斷屏蔽位是第7位和第6位(I和F),當I或F設為1時irq或fiq就被屏蔽了.

condtion flags:condition flags可以被比較操作和帶S后綴的ALU操作來更新.

四、異常 中斷和向量表

當異常發生時,處理器會將pc指向一個特殊的內存地址.該地址所在的地址范圍稱為向量表.向量表的入口是跳轉指令,跳轉到專門處理某個異常或中斷的子程序.

存儲器映射地址0x00000000是為向量表預留的.在某些處理器中向量表可以放在更高的地址,從0xffff0000開始.linux等操作系統可以利用這個特性.

當異常發生時,處理器掛起正常的處理然后從向量表中加載指令.每個向量表的入口都包含指向特殊處理例程的跳轉指令.

reset向量是處理器上電后執行的第一條指令,這條指令跳轉到初始化代碼處.

undefined instruction向量是當處理器不能對指令譯碼時使用的.

software interrupt向量執行SWI指令時使用的.SWI可以用來系統調用的實現.

prefetch abort向量發生在當沒有訪問權限的條件下試圖獲取該地址的指令時,異常發生在譯碼階段.

data abort向量與prefetch abort類似,只不過是訪問數據發生的異常.

interrupt request向量被外部硬件用來中斷處理器的正常執行.只有在cpsr的相應位為0時才能發生.

fast interrupt request向量與irq類似,是為要求更短的中斷響應時間的硬件保留的.只有在cpsr的相應位為0時才能發生.

五、流水線

RISC處理器用流水線機制來執行指令.ARM流水線中的指令只有在完全通過執行階段才被處理.

上面這張圖標明了流水線的使用和程序計數器pc.在執行階段,pc總是指向該指令地址加上8字節.也就是說pc總是指向當前指令的下下條指令.當用pc來計算

相對偏移量時這點是很重要的,并且它也是所有流水線的特征.

六、條件執行:

條件執行控制指令是否被ARM核執行.處理器會比較指令的條件屬性和cpsr中的condition flags,如果匹配,該指令執行;否則該指令被忽略.

評論