ARM裸機開發bootloader時鐘初始化ARM跑快了

1、什么是時鐘脈沖信號,起什么作用?

本文引用地址:http://cqxgywz.com/article/201611/318215.htm時鐘脈沖信號時有一定電壓幅度和一定的時間間隔并連續發出的脈沖信號。時鐘脈沖信號是時序邏輯的基礎,它用于決定邏輯單元中的狀態何時更新。數字芯片中的眾多晶體管都工作在開關狀態,它們的導通和關斷動作都是按照時鐘信號的節奏進行的。也就是說嵌入式系統是按照時鐘來安排CPU的任務。

2、時鐘脈沖信號的頻率是指單位時間內產生的時鐘脈沖個數。

3、如何產生時鐘信號?

時鐘信號一般有晶振或晶振與PLL產生。

晶振的制造就是用石英晶體經精密切割磨削并鍍上電極焊上引線就做成了。這種晶體如果給它通上電,它就會產生機械振蕩,其頻率和他們的形狀,材料,切割方向等密切相關。

由于石英晶體化學性能非常穩定,熱膨脹系數非常小,其振蕩頻率也非常穩定,由于控制幾何尺寸可以做到很精密,因此,其諧振頻率也很準確。

4、晶振和鎖相環(PLL)

晶體振蕩器時鐘的優點:結構簡單,噪聲低。缺點:由于其頻率僅由晶體決定,通常是特定晶體被制成客戶所需要的振蕩器,導致生產成本高、交貨周期較長,不利于客戶加快產品上市時間,而且難以獲得非標準的頻率。

PLL(鎖相環)合成器是一種更為復雜的系統時鐘源。通用的PLL合成器需要一個外部晶體并包含一個能夠對晶體的特定頻率加倍或分頻的集成鎖相環(PLL)電路。

5、信號產生對比

5.1、對于特定的時鐘頻率,采用PLL合成器可以使用較便宜以及較低頻率晶振來代替昂貴的高頻晶振;

5.2、對于需要多個時鐘頻率的系統,采用PLL合成器通過分頻即可實現,而此時采用晶振模塊則需要多個不同頻率的晶振。

因此相對于晶體振蕩器模塊,通過PLL合成器提供精確時鐘具有成本更低、占板面積更小等一系列優點。

二、時鐘體系

學習時鐘體系學什么

1、晶振頻率 2、PLL 3、PLL產生了哪些時鐘 4、產生的時鐘是提供給誰的

2440:

1、12MHZ晶振

2、MPLL、UPLL

3、MPLL(FCLK,HCLK,PCLK)

UPLL(UCLK)

4、

| 時鐘 | 應用場合 | 應用舉例 |

| FCLK | 處理器 | ARM9 |

| HCLK | AHB BUS | LCD DMA |

| PCLK | APB BUS | UART GPIO |

| UCLK | USB | USB主從口 |

APB是低帶寬的周邊外設之間的連接總線

DMA的概念:DMA(Direct memory access)是在專門的硬件( DMA)控制下,實現高速外設和主存儲器之間自動成批交換數據盡量減少CPU干預的輸入/輸出操作方式。

6410:

1、12MHZ

2、APLL、MPLL、EPLL

3、APLL(ARMCLK) MPLL(HCLK PCLK) EPLL(SCLK)

4、

| 時鐘 | 應用場合 | 應用舉例 |

| ARMCLK | ARM | ARM11 |

| HCLK | AHB BUS | LCD DMA |

| PCLK | APB BUS | UART GPIO |

| SCLK | 特殊情況 | USB主從口 |

210:

1、24MHZ

2、4個PLL:APLL,MPLL,EPLL,VPLL

3、210與2440和6410都有所不同:

| 時鐘體系 | 所屬時鐘 | 應用舉例 | 鎖相環 |

| MSYS | ARMCLK HCLK_MSYS PCLK_MSYS | ARM核 內存控制器 中斷 | APLL |

| DSYS | HCLK_DSYS PCLK_DSYS | 顯示相關部件,如FIMC | MPLL |

| PSYS | HCLK_PSYS CLK_DPM | 外設,如Uart,i2C | EPLL |

| 視頻相關 | VPLL |

三、思維導圖的設計

軟件設計指導:

1、時鐘初始化流程

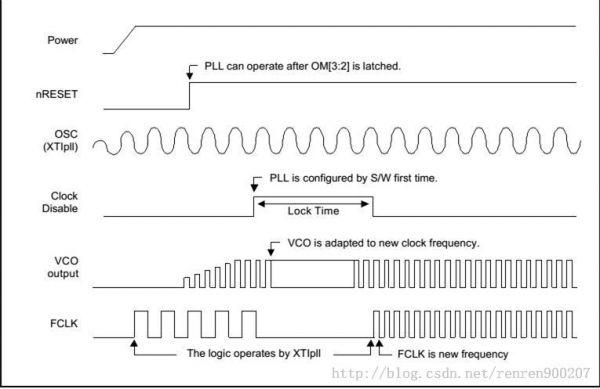

從上圖的時序我們可以看到

1、上電幾毫秒后,晶振輸出穩定,FCLK=晶振頻率,nRESET信號恢復高電平后,CPU開始執行指令。

2、我們的程序開頭啟動MPLL,設置MPLL的寄存器

3、在設置MPLL的寄存器后,需要等待一段時間(Lock Time),MPLL的輸出才穩定。在這段時間(Lock Time)內,FCLK停振,CPU停止工作。Lock Time的長短由寄存器LOCKTIME設定。

4、Lock Time之后,MPLL輸出正常,CPU工作在新的FCLK下。

時鐘初始化流程(芯片手冊):

1、設置Lock Time

2、設置分頻系數

3、設置CpU到異常模式

4、設置FCLK

開始寫代碼

2440:

1、在芯片手冊查找Locktime -register,一般我們都使用默認值,所以可以忽略不做

2、設置分頻系數

參考Uboot中的分頻系數為FCLK:HCLK:PCLK = 1:4:8

時鐘初始化程序要位于led點亮程序之前,這樣便于調試。

#define CLKDIVN 0x4c0000004

clock_init:

ldr r0, =CLKDIVN

mov r1, 0x5

str r1, [r0]

3、設置CPU到異步工作模式

mrc p15, 0, r0, c1, c0, 0

orr r0, r0, 0xc0000000

mcr p15, 0, r0, c1, c0, 0

4、設置FCLK

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<<12) | (2<<4) | (1<<0))

ldr r0, =MPLLCON

mov r1, =MPLL_405MHZ

str r1, [r0]

mov pc, lr

6410:

1、同樣,Lock time不變,保持原來值。

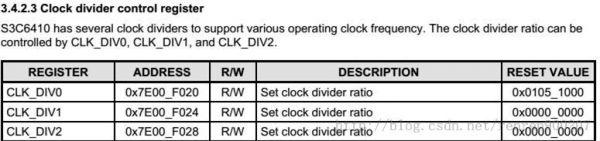

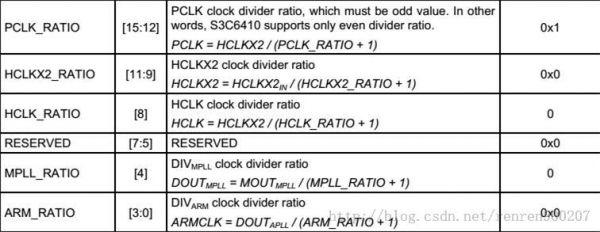

2、設置分頻系數

ARMCLK = APLLout/(DIVARM+1)HCLKX2 = MPLLout/(DIVHCLKX2+1)HCLK = HCLKX2/(DIVHCLK+1)PCLK = HCLKX2/(DIVPCLK+1)

參考Uboot可以設置DIVpclk = 3 DIVhclk = 1 DIVhclkX2 = 1 DIVARM = 0

代碼如下:

#define CLK_DIV0 0x7e00f020#define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12))init_clock:ldr r0, =CLK_DIV0ldr r1, = DIV_VALstr r1, [r0]

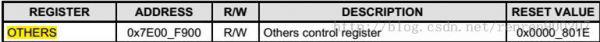

3、設置CPU工作在異常模式下

#define OTHERS 0x7e00f900ldr r0, =OTHERSldr r1, [r0]bic r1, r1, #0xc0str r1, [r0]

4、設置FCLK為533MHZ

#define MPLL_CON, 0x7e00f010#define APLL_CON, 0x7e00f00c#define PLL_Val ((1<<31)|(266<<16)|(3<<8)|(1<<0))ldr r0, =APLL_CONldr r1, =PLL_Valstr r1, [r0]ldr r0, =MPLL_CONldr r1, =PLL_Valstr r1, [r0]

5、6410還有個特殊性就是設置一下選擇器CLK_SRC設置PLL產生時鐘為時鐘源。

#define CLK_SRC 0x7e00f01cldr r0, =CLK_SRCmov r1, #0x3str r1, [r0]然后運行后下載到開發板運行

全代碼為:

.text.global _start_start:b resetldr pc, _undefined_instructionldr pc, _software_interruptldr pc, _prefetch_abortldr pc, _data_abortldr pc, _not_usedldr pc, _irqldr pc, _fiq_undefined_instruction: .word undefined_instruction_software_interrupt: .word software_interrupt_prefetch_abort: .word prefetch_abort_data_abort: .word data_abort_not_used: .word not_used_irq: .word irq_fiq: .word fiqundefined_instruction:nopsoftware_interrupt:nopprefetch_abort:nopdata_abort:nopnot_used:nopirq:nopfiq:nopreset:bl set_peri_portbl set_svcbl disable_watchdogbl disable_interruptbl disable_mmubl init_clockbl light_ledset_peri_port:ldr r0, =0x70000000orr r0, r0, #0x13mcr p15,0,r0,c15,c2,4mov pc, lr set_svc:mrs r0, cpsrbic r0, r0, #0x1forr r0, r0, #0xd3msr cpsr, r0mov pc, lr#define pWTCON 0x7E004000disable_watchdog:ldr r0, =pWTCON /*mov的操作數最多為8位*/mov r1, #0x0str r1, [r0]mov pc, lrdisable_interrupt:mvn r1, #0x0ldr r0, =0x71200014str r1, [r0]ldr r0, =0x71300014str r1, [r0]mov pc, lrdisable_mmu:mcr p15, 0, r0, c7, c7, 0mrc p15, 0, r0, c1, c0, 0bic r0, r0, #0x00000007mcr p15, 0, r0, c1, c0, 0mov pc, lr #define CLK_DIV0 0x7e00f020#define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12))#define OTHERS 0x7e00f900#define MPLL_CON 0x7e00f010#define APLL_CON 0x7e00f00c#define PLL_Val ((1<<31)|(266<<16)|(3<<8)|(1<<0))#define CLK_SRC 0x7e00f01cinit_clock:ldr r0, =CLK_DIV0ldr r1, =DIV_VALstr r1, [r0]ldr r0, =OTHERSldr r1, [r0]bic r1, r1, #0xc0str r1, [r0]ldr r0, =APLL_CONldr r1, =PLL_Valstr r1, [r0]ldr r0, =MPLL_CONldr r1, =PLL_Valstr r1, [r0]ldr r0, =CLK_SRCmov r1, #0x3str r1, [r0]mov pc, lr #define GPKCON0 0x7f008800#define GPKDAT 0x7f008808light_led:ldr r0, =GPKCON0ldr r1, =0x11110000str r1, [r0]ldr r0, =GPKDATldr r1, =0xa0str r1, [r0]mov pc, lr

評論