單片機關鍵技術基礎詳解(一)

一、關于C51單片機的中斷號以及中斷向量

1、中斷號

2、interrupt 和 using 在C51中斷中的使用

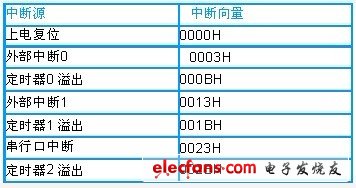

8051 系列 MCU 的基本結構包括:32 個 I/O 口(4 組8 bit 端口);兩個16 位定時計數器;全雙工串行通信;6 個中斷源(2 個外部中斷、2 個定時/計數器中斷、1 個串口輸入/輸出中斷),兩級中斷優先級;128 字節內置RAM;獨立的 64K 字節可尋址數據和代碼區。中斷發生后,MCU 轉到 5 個中斷入口處之一,然后執行相應的中斷服務處理程序。中斷程序的入口地址被編譯器放在中斷向量中,中斷向量位于程序代碼段的最低地址處,注意這里的串口輸入/輸出中斷共用一個中斷向量。8051的中斷向量表如下:

二、CPU與單片機的復位電路的作用及基本復位方式

在上電或復位過程中,控制CPU的復位狀態:這段時間內讓CPU保持復位狀態,而不是一上電或剛復位完畢就工作,防止CPU發出錯誤的指令、執行錯誤操作,也可以提高電磁兼容性能。

無論用戶使用哪種類型的單片機,總要涉及到單片機復位電路的設計。而單片機復位電路設計的好壞,直接影響到整個系統工作的可靠性。許多用戶在設計完單片機系統,并在實驗室調試成功后,在現場卻出現了“死機”、“程序走飛”等現象,這主要是單片機的復位電路設計不可靠引起的。

基本的復位方式

單片機在啟動時都需要復位,以使CPU及系統各部件處于確定的初始狀態,并從初態開始工作。89系列單片機的復位信號是從RST引腳輸入到芯片內的施密特觸發器中的。當系統處于正常工作狀態時,且振蕩器穩定后,如果RST引腳上有一個高電平并維持2個機器周期(24個振蕩周期)以上,則CPU就可以響應并將系統復位。單片機系統的復位方式有:手動按鈕復位和上電復位。

1、手動按鈕復位

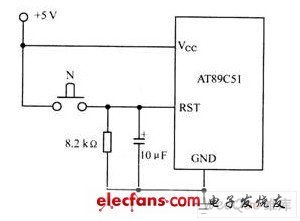

手動按鈕復位需要人為在復位輸入端RST上加入高電平(圖1)。一般采用的辦法是在RST端和正電源Vcc之間接一個按鈕。當人為按下按鈕時,則Vcc的+5V電平就會直接加到RST端。手動按鈕復位的電路如所示。由于人的動作再快也會使按鈕保持接通達數十毫秒,所以,完全能夠滿足復位的時間要求。

圖1

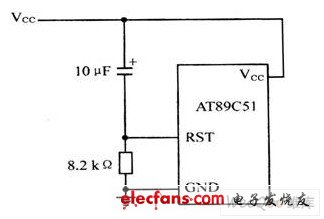

2、上電復位

AT89C51的上電復位電路如圖2所示,只要在RST復位輸入引腳上接一電容至Vcc端,下接一個電阻到地即可。對于CMOS型單片機,由于在RST端內部有一個下拉電阻,故可將外部電阻去掉,而將外接電容減至1?F。上電復位的工作過程是在加電時,復位電路通過電容加給RST端一個短暫的高電平信號,此高電平信號隨著Vcc對電容的充電過程而逐漸回落,即RST端的高電平持續時間取決于電容的充電時間。為了保證系統能夠可靠地復位,RST端的高電平信號必須維持足夠長的時間。上電時,Vcc的上升時間約為10ms,而振蕩器的起振時間取決于振蕩頻率,如晶振頻率為10MHz,起振時間為1ms;晶振頻率為1MHz,起振時間則為10ms。在圖2的復位電路中,當Vcc掉電時,必然會使RST端電壓迅速下降到0V以下,但是,由于內部電路的限制作用,這個負電壓將不會對器件產生損害。另外,在復位期間,端口引腳處于隨機狀態,復位后,系統將端口置為全“l”態。如果系統在上電時得不到有效的復位,則程序計數器PC將得不到一個合適的初值,因此,CPU可能會從一個未被定義的位置開始執行程序。

圖2

3、積分型上電復位

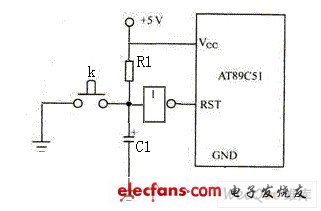

常用的上電或開關復位電路如圖3所示。上電后,由于電容C3的充電和反相門的作用,使RST持續一段時間的高電平。當單片機已在運行當中時,按下復位鍵K后松開,也能使RST為一段時間的高電平,從而實現上電或開關復位的操作。

根據實際操作的經驗,下面給出這種復位電路的電容、電阻參考值。

圖3中:C:=1uF,Rl=lk,R2=10k

圖3 積分型上電復位電路

三、單片機雙機并行通信中所遇問題

1 引言

本系統采用的CPLD為 ATMEL公司生產的ATF1540AS器件,該器件是一種高性能、高密度復合可編程邏輯器件,簡稱CPLD,它利用ATMEL 的電可擦除存儲器技術,有 64個邏輯宏單元和68個I/O端口,很容易和多個TTL、SSI、MSI、LSI和經典的PLDS組合使用。每個宏單元包括積項和積項多路選擇器、 OR/XOR/CASCADE邏輯、觸發器、輸出選擇和使能、輸入邏輯陣列五個部分。ATF1504AS的增強選路開關增加了可用的門計數,提高了管腳鎖存設計修改的成功率。

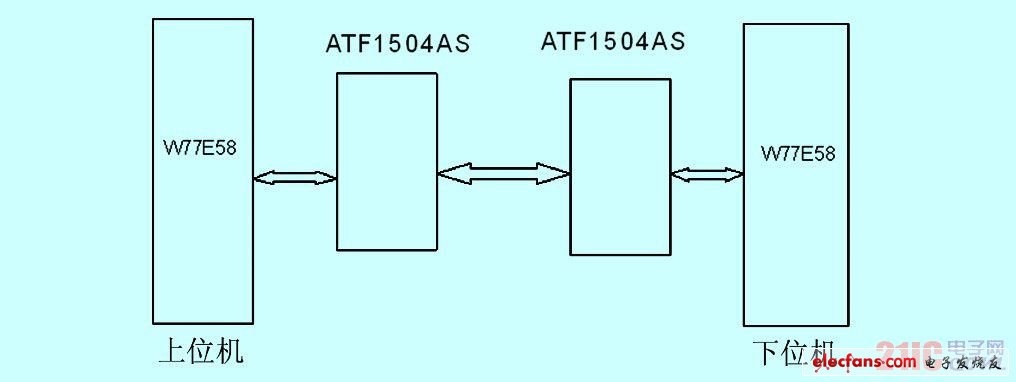

圖1 雙機通信框圖

2 系統結構

系統的CPU采用W77E58,由ATF1504AS構成通信接口,系統框圖如圖1所示。

2.1 問題提出

電腦刺繡機為達到良好的人機界面交互功能,采用上下位機方式,下位機主要進行繡花動作的控制,上位機主要進行花樣的跟蹤。為了實現繡花的同時在液晶屏上進行繡花跟蹤,單CPU方式存在系統資源透支, CPU處理數據將十分困難,于是提出了采用雙CPU的工作方式,但同時帶來一個問題—雙CPU的通信問題。

2.2 解決方案

(1) 采用串行通信方式

優點:在由單片機組成的多機方式中,串行接口方式是最常用的。串行通信方式接口電路簡單,可以方便實現長距離傳輸。抗干擾能力比較好。

缺點:傳輸數據慢,不適合實時數據傳輸。在數據傳輸要求高的情況下,容易造成瓶頸堵塞現象。

(2) 采用并行通信方式

優點:并行通信傳輸數據快,適合進行實時控制。

缺點:抗干擾能力差,不適合長距離傳輸,最大距離不超過5m。

由于本系統對數據傳輸的實時性要求比較高,并且上下位機之間的距離不超過3m,進行適當的抗干擾措施,完全可以達到系統的要求,所以確定采用并行通信方式。

2.3 具體措施

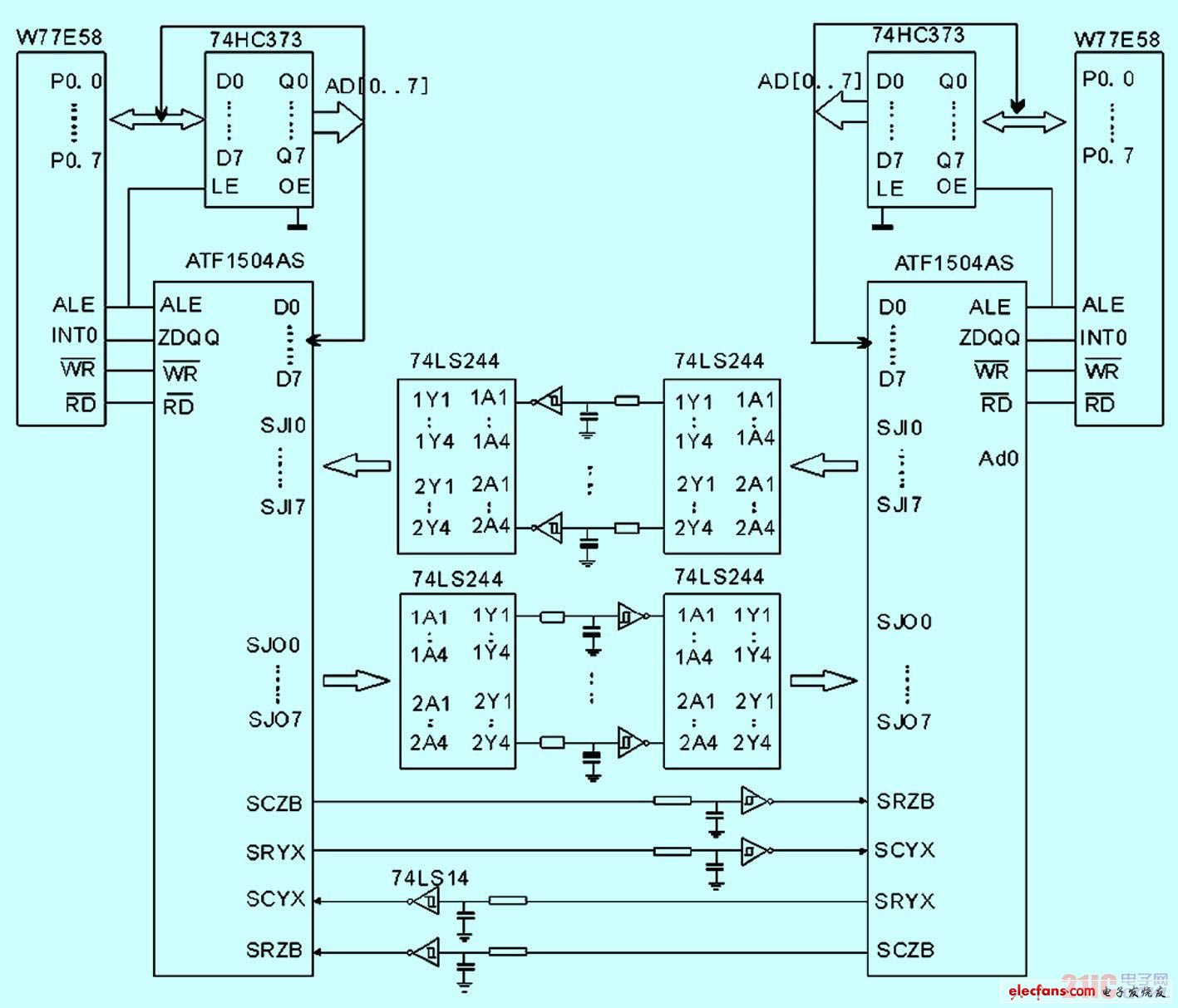

(1) 采用ATF1504AS(可編程邏輯器件)進行并行通信,減少分立器件所產生的雜散電容而帶來的噪聲干擾。

(2) 在輸入數據端加斯密特電路(74LS14),將外部傳輸線上耦合噪聲濾除掉。從而提高總線接收的抗干擾性能。

(3)采用三態門驅動方式可以提高總線的抗干擾能力,因為三態門有三種狀態輸出,既所謂的低阻高電平、低阻低電平、高阻態(禁態)。由于三態門的輸入具有的三態性,所以使三態門的信號源的負擔減輕。有利于提高速度和抗干擾能力。

3 雙CPU通信原理設計

3.1 雙CPU通信原理圖

從圖2雙CPU通信原理圖中可以看出,在輸入接口上都接上74LS14斯密特電路和74LS244三態門驅動器,以提高抗干擾能力。在SRZB、SCYX(上位機)及SRZB、SCYX(下位機)的握手信號線上接入74LS14斯密特電路,以提高抗干擾能力。

圖2 雙機通信原理圖

3.2 ATF1504AS內部原理圖

由于篇幅有限,僅列出上位機的ATF1504AS的內部原理圖如圖3,下位機的ATF1504AS的內部原理圖與此相類似。

評論