上拉電阻和下拉電阻的選擇

這個提法基本是對的,但也不全對。下面詳細加以說明。

本文引用地址:http://cqxgywz.com/article/201611/321948.htm管腳上拉下拉電阻設計出發點有兩個:

一個是在正常工作或單一故障狀態下,管腳均不應出現不定狀態,如接頭脫落后導致的管腳懸空;

二是從功耗的角度考慮,就是在長時間的管腳等待狀態下,管腳端口的電阻上不應消耗太多電流,尤其是對電池供電設備。

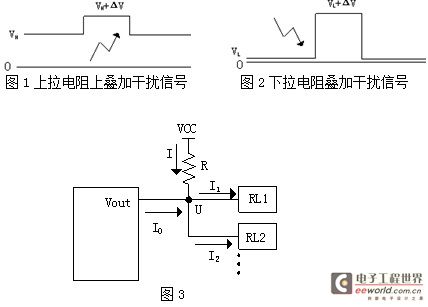

從抗擾的角度,信號端口優選上拉電阻。上拉電阻時,在待機狀態下,源端輸入常為高阻態,如果沒有上拉電阻或下拉電阻,輸入導線呈現天線效應,一旦管腳受到輻射干擾,管腳輸入狀態極容易被感應發生變化。所以,這個電阻是肯定要加的。下一個問題就是加上拉還是下拉。

如果加了下拉,在平常狀態下,輸入表現為低電平,但輻射干擾進來后,會通過下拉電阻瀉放到地,就會發生從Low—High的一個跳變,產生誤觸發。相當于一個乞丐,你給了他10萬元,他的生活方式就會從窮人到富人發生一個改變。

但如果加了上拉電阻,在平常狀態下,輸入表現為高電平,輻射干擾進來后,如果低也沒關系,上拉電阻會將輸入端鉗位在高電平,如果輻射干擾強,超過了Vcc的電平,導線上的高電平干擾會通過上拉電阻瀉放到Vcc上去,無論怎樣干擾,都只會發生High—Higher的變化,不會產生誤觸發。相當于人家本來是一個富豪,你給了他10萬元,他的生活方式不會發生任何的改變。

A、當I0>= I1+ I2

B、當I0< I1+ I2

以上三式可以得出:R>=(VCC- VLmax)/I’

評論