TQ2440國嵌學院gboot-時鐘初始化

1:設(shè)置lock time寄存器

本文引用地址:http://cqxgywz.com/article/201611/321970.htm2:設(shè)置分頻系數(shù)(FCLK:HCLK:PCLK)

3:設(shè)定CPU到異步模式(通常FCLK不等于HCLK)

4:設(shè)置FCLK

首先了解下CPU的時鐘分類:

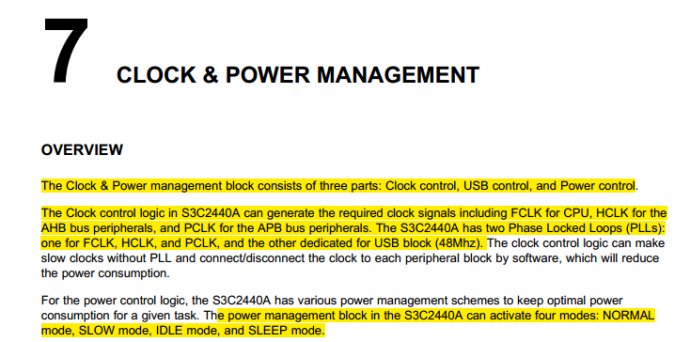

同樣在S3C2440中找到CLOCK第7章這一章如下:

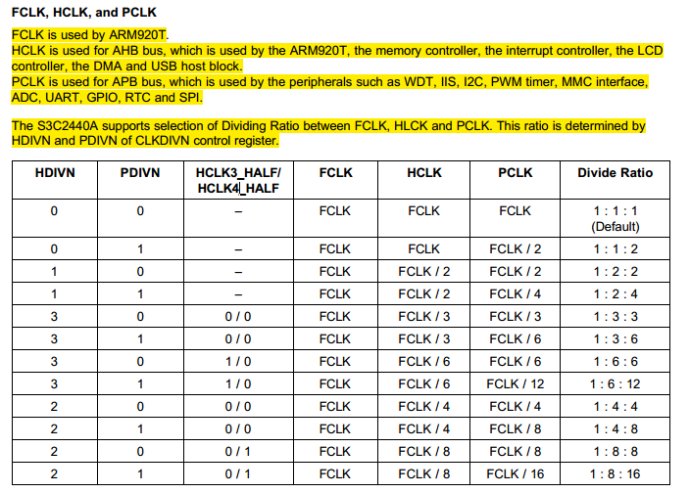

從上面的文字中,可以得到FCLK主要是CPU核的工作時鐘,HCLK是AHB總線(LCD,DMA)的工作時鐘,PCLK是APB總線(UART,GPIO)工作時鐘。

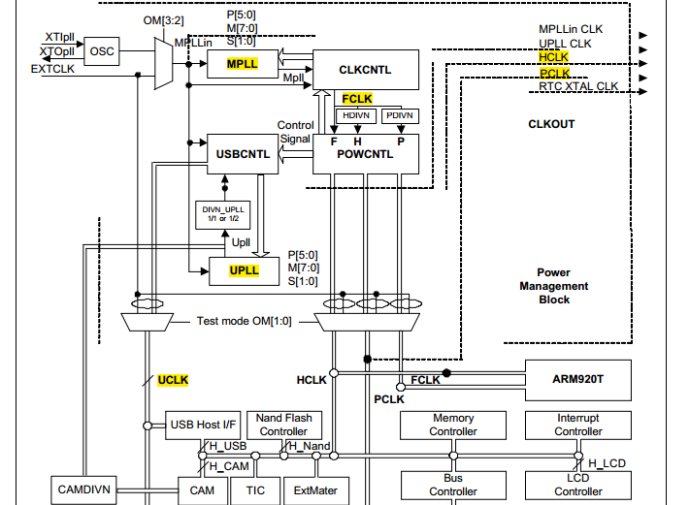

下面是CPU內(nèi)部時鐘電路結(jié)構(gòu)圖

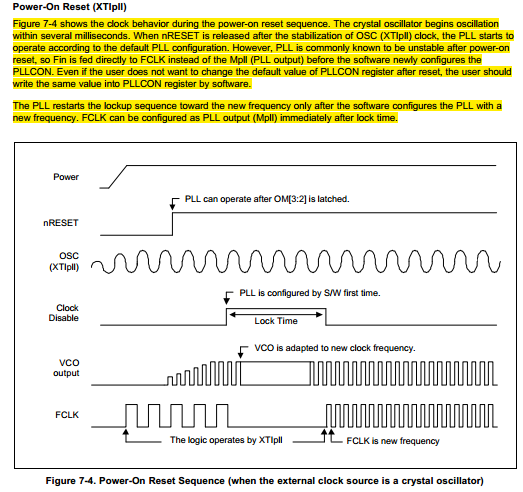

其次是CPU的啟動時鐘時序:

從上圖可以看出,在上電后,nRESET會拉高,clock開始起振輸出時鐘信號,此時CPU工作在12MHz,然后PLL開始進入軟體設(shè)置,這時候FCLK為0,沒有時鐘信號供CPU工作,當然時間很短,當PLL設(shè)定后FCLK以新的時鐘頻率供CPU工作。

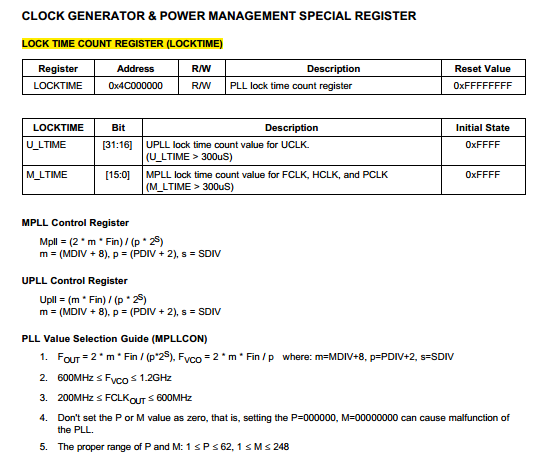

LOCK TIME寄存器設(shè)定:

通常情況下不設(shè)定,采用默認值。

再次如何設(shè)定分頻系數(shù)呢?如下圖

評論