基于FPGA的數字鎖相環平臺的搭建

基于鎖相環的理論,以載波恢復環為依托搭建數字鎖相環平臺,并在FPGA中實現鎖相環的基本功能。

本文引用地址:http://cqxgywz.com/article/201612/326341.htm在FPGA中實現鎖相環的自動增益控制,鎖定檢測,鎖定時間、失鎖時間的統計計算,多普勒頻偏的估計。

通過USB接口與電腦實現通信來交換有關鎖相環的參數。電腦傳遞鎖相環所需的參數(如等效噪聲帶寬等),FPGA將鎖相環的結果傳遞給電腦(如鎖定時間,多普勒頻率等)。

二、設計任務

鎖相環的輸入具有自動增益控制AGC模塊,這樣可以允許一定動態范圍的信號輸入,也減少了輸入環路信噪比的大幅波動,從而減少了環路噪聲帶寬的大幅波動。

基于VHDL語言實現數字鎖相環,混頻基于CORDIC算法,相位提取模塊是修正的反正切相位提取,環路濾波器采用理想的二階環,NCO采用32位的累加器。設計完先進行Modelsim仿真,后利用ISE自帶的CHIPSCOPE下載調試。

具有鎖定檢測模塊,當環路鎖定時,通過LED燈或數碼管給出鎖定指示。

通過鎖定指示的輸出信號,來控制一個實時時鐘,這樣可以統計鎖定時間和失鎖時間,所記錄的時間存入兩個FIFO。

設計USB通信模塊,使得設計的鎖相環可以同電腦進行通信,將接收電腦傳給FPGA的環路參數,同時將檢測的鎖定時間和失鎖時間,鎖定指示,多普勒頻偏估計等傳輸給電腦。

利用MATLAB GUI設計一個控制面板,通過控制面板可以隨時改變鎖相環的環路參數,也可以接收鎖相環通過USB傳輸給電腦的鎖相環的結果。

三、設計原理

隨著數字技術的發展,現在出現了很多資源豐富的可編程器件,像FPGA、DSP、專用集成電路等,基于軟件無線電的通信系統,一般采用數字鎖相環。數字鎖相環具有鎖定精度高,跟蹤帶寬大,參數可以在不修改硬件電路的前提下進行修改等種種的優點。目前,數字鎖相環廣泛應用于通信、航天等領域。針對具體的應用,數字鎖相環可以用于載波跟蹤,相位提取等。本設計就是以載波回復環為依托進行的數字鎖相環設計。

(1)、鎖相環的基本框架

鎖相環是一個頻率與相位的同步控制系統。它的工作過程可用下圖表示

上面的鎖相環是一般模擬鎖相環所必需包含的環路組成,包括鑒相器、環路濾波器、壓控振蕩器。而對于利用軟件來實現的全數字鎖相環,必須在FPGA內部實現鎖相環的鑒相器、環路濾波器、壓控振蕩器等部件。

(2)、本設計所要實現的鎖相環的基本框架

本設計中,鑒相器有CORDIC混頻器加上修正的arctan相位提取器組成,環路濾波器有理想二階環組成,NCO由32位的數字累加器組成。

下面就比較重要的幾個模塊進行介紹

1、數字前端AGC模塊

數字前端模塊的框圖如下:

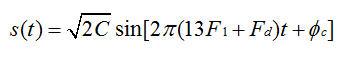

數字前端模塊接收來自ADC的采樣數據,然后分成兩路輸出給載波恢復模塊。輸入到ADC的模擬信號頻率為

,ADC的采樣頻率為![]() 。這種IQ采樣過程把ADC的輸出數據頻譜搬移到

。這種IQ采樣過程把ADC的輸出數據頻譜搬移到![]() 附近。在數字前端模塊中,把輸入的數據分成I、Q兩路,然后數字混頻到基帶。這個數字混頻只是簡單的乘上頻率為

附近。在數字前端模塊中,把輸入的數據分成I、Q兩路,然后數字混頻到基帶。這個數字混頻只是簡單的乘上頻率為

序列,不會產生二次頻,因此后續不需要濾波處理。信號處理過程的數學表達式如下,假定ADC的中頻輸入信號為一簡單的正弦波:

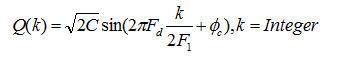

ADC的輸出為:

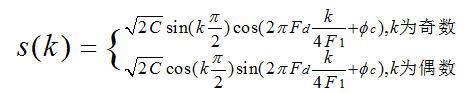

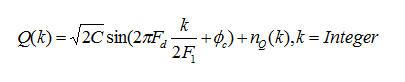

經奇偶分離和數字混頻后,輸出的I、Q兩路信號分別為:

這兩路信號在頻域上存在2F1頻率附近的頻譜,因此必須把這個頻譜消除掉。本設計采用了直接抽去掉0的方法,抽取后I,Q兩路信號的數據速率從4F1降到了2F1。

經抽取后的兩路信號分別為:

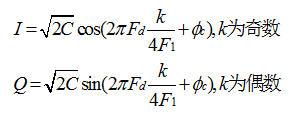

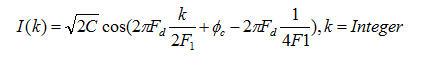

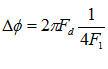

從上兩式可見,直接抽取的方法會使I、Q兩路信號之間存在一個跟采樣頻率及多普勒頻偏有關的固定相位偏差

但是由于

因此這個偏差非常小,在本設計中就不考慮這個固定偏差了。于是

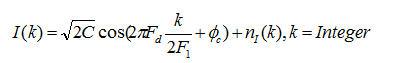

其中![]() 和

和![]() 都為零均值的高斯噪聲,且互不相關,方差為

都為零均值的高斯噪聲,且互不相關,方差為![]() ,其中

,其中![]() 是單邊帶噪聲功率譜密度。

是單邊帶噪聲功率譜密度。

一般載波跟蹤環要工作在很大的動態范圍下,為了使環路帶寬和阻尼系數變化范圍不要太大,從而使環路處于正常的工作狀態下,必須控制環路內的信號強度,因為環路帶寬和阻尼系數與信號強度有關。

AGC使信號可以保持一個近乎恒定的信號強度,增大了環路的動態范圍,影響的是信號的功率或幅度,而對于相位幾乎沒有影響。AGC是采用了相干AGC的處理方法,由于它對于相位無影響,它的作用只是輸出一個幅度盡量恒定的信號,因此這里就不討論AGC的算法了。2、CORDIC 混頻器

CORDIC是一種迭代的算術計算算法,通過相位旋轉的方式能求各種基本函數的值。基于移位-相加方式實現的CORDIC算法是一種高效的硬件處理算法,非常適合在FPGA中應用。直角坐標系中,旋轉矢量[x, y]和相位 的關系圖如下:

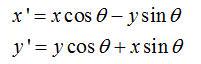

其方程如下:

上式可改寫為:

如果把旋轉的角度限定為

,即

,

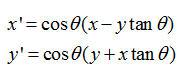

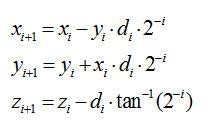

上式中與正切相乘的算法就簡化為移位操作,因此迭代的旋轉算法可以表示為:

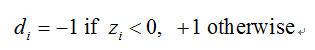

其中:

以上方程在硬件中實現非常簡單,因為乘 操作可以通過右移來實現。

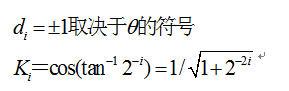

把增益因子![]() 從迭代方程中移除,基于移位-相加的CORDIC算法方程如下:

從迭代方程中移除,基于移位-相加的CORDIC算法方程如下:

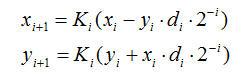

其中:

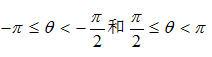

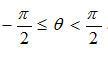

以上方程在

范圍內的任意角度都能收斂。如果要在整個直角坐標系上工作,還必須把

映射到

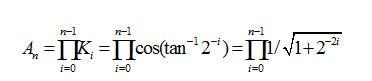

。此外,還必須補償增益因子,定義![]() 為:

為:

其中n是CORDIC算法的迭代計算次數。![]() 的值取決于迭代次數n,在n確定的情況可以視為一個常數。當n趨于無窮大時,

的值取決于迭代次數n,在n確定的情況可以視為一個常數。當n趨于無窮大時,![]() 的值為0.60725。因為

的值為0.60725。因為![]() 和

和![]() 是常數,可以預先存在一個很小的查找表里。

是常數,可以預先存在一個很小的查找表里。

3、環路設計及分析

基于跟蹤性能和穩定性的折中考慮,接收機一般采用二階環。在本設計中,我們采用了理想型積分環路濾波器。理想型積分環路濾波器的鎖相環有更佳的跟蹤性能,在固定頻偏下,無穩態相位誤差。

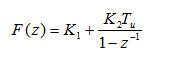

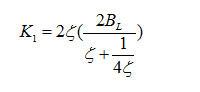

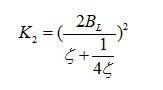

一階理想型積分環路濾波器的數字域表達式:

四、設計仿真

用MATLAB軟件搭建鎖相環的核心仿真平臺,包括中頻欠采樣,數字前端分成I、Q兩路信號,AGC,CORDIC混頻,積分抖落濾波器,修正的正切相位提取器,環路濾波器,NCO,鎖定檢測等。

(1)、系統框圖

(2)、仿真結果

1、AGC的仿真,輸入AGC的I、Q兩路信號幅度為0.01V Vpp,從仿真圖中可用看出AGC輸出的幅度為1V Vpp,鎖定時間在3ms左右。

2、相位誤差以及多普勒頻偏的估計的仿真,在仿真中我們設定的多普勒頻偏為1kHz,從下圖的仿真結果鎖定后的相位誤差非常小,所得到的多普勒頻偏的估計也恰好為1KHz。

評論