CMOS欠壓保護電路的設計方案分析

1.引言

本文引用地址:http://cqxgywz.com/article/201612/327525.htm在電機驅動、UPS等系統中電壓的穩定尤為重要,欠壓、過壓保護是必不可少的,因此通過在芯片內部集成過壓、欠壓保護電路來提高電源的可靠性和安全性。對功率集成電路,為提高電路的可靠性,保護電路同樣必不可少。保護電路的設計要簡單、實用,本文設計了一種CMOS 工藝下的欠壓保護電路,此電路結構簡單,工藝實現容易,可用做高壓或功率集成電路等的電源保護電路。

2.工作原理分析

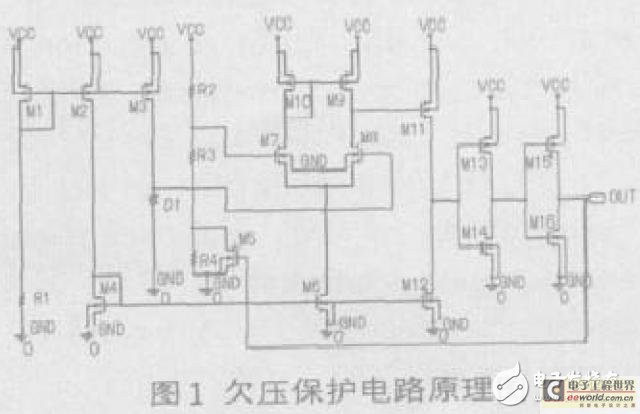

欠壓保護的電路原理圖如圖1 所示。共由五部分組成:偏置電路、基準電壓產生、欠壓檢測輸入、比較器、反饋回路。

本電路的電源電壓是15V,M1、M2、M4、R1 是電路的偏置部分,給后級電路提供偏置,電阻R1 決定了電路的工作點,M1、M2、M4 是電流鏡;M3、D1產生基準電壓,輸入比較器的同相端;分壓電阻R2、R3、R4是欠壓檢測輸入,輸入比較器的反相端;R4、M5是欠壓信號的反饋回路;其余M6~M16 組成四級放大比較器。

M3、D1 產生基準電壓,輸入比較器的同相端,固定不變是11V,當電源電壓正常工作時,反相端的欠壓檢測輸給比較器的反相端的電壓大于11V,比較器輸出為低,M5截止,反饋電路不起作用;當欠壓發生時,分壓電阻R2、R3、R4 反映比較敏感,當電阻分壓后輸給反相端的電壓小于11V,比較器的輸出電壓為高,此信號將M5 開啟,使得R4兩端的電壓變為M5兩端的飽和電壓,趨近于0V,從而進一步拉低了R2、R3 分壓后得輸出電壓,形成了欠壓的正反饋。輸出為高,欠壓鎖定,起到了保護作用。

3.參數計算

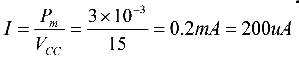

對于MOS模擬集成電路,各MOS管的工作狀態和管子尺寸及寬長比決定了電路的功能和性能,下面結合0.6μm工藝,對電路的電阻及各管寬長比進行估算。設定電路的總功耗Pm《3mW,VCC是15V,將Uth近似為1V。根據總功耗可得總電流:

電路共有八條回路(200/8),可大致分配各路電流20 μ A 左右:故偏置電流20 μ A,即:電阻R1 的阻值大致約;

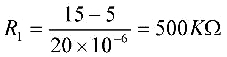

電路中MOS 管均工作在飽和區,MOS 管的飽和區的公式:

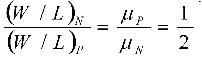

可以估算出M1 的寬長比,進而由電流鏡和PMOS 、NMOS的寬長比與遷移率的關系

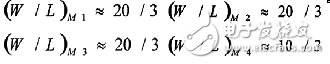

可得M2、M3、M4 的比值,即:

穩壓管的電壓值的設定要考慮工藝的實現并且要滿足M3 工作在飽和區的條件下選定,這里電壓值選為11V;而電阻的設計要考慮面積因素。電阻R2、R3、R4 構成分壓器,設定此路中電流是30 μ A,忽略M5 的電阻,可得

其中,R3=300KΩ,R4=70KΩ

比較器的增益要足夠的大,設定比較器的開環增益在80dB(104 倍)以上,由于實際制作出的產品往往比理論計算出的放大倍數小很多。因此,我們分配各級的放大倍數分別: Aμ1=50,Aμ2=20,Aμ3=10.總共的放大倍數為各級放大倍數的乘積,即為:

分配各級電流的四路總和不超過110μA(200μA-20×3μA-30μA)。故分配各級電流分別為30 μ A、20 μA、30 μA 和30 μA。這樣,我們就可以根據放大倍數和偏置電流來計算出各個管子的寬長比。

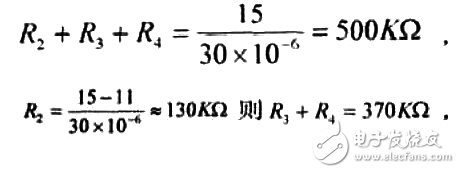

對于差分放大級。放大倍數Aμ1=50, 偏置電流為30μA,則兩個支路的電流為1 5 μ A 。根據計算公式:

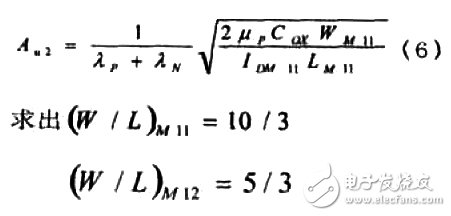

第二級,共源放大級。放大倍數A μ2=20,流過的電流為20 μ A,根據

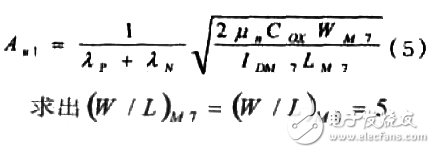

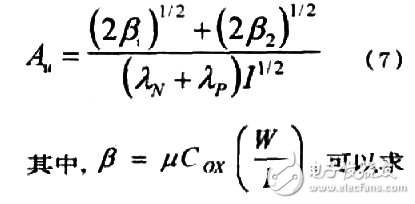

第三級和第四級推挽CMOS 放大級,由公式:

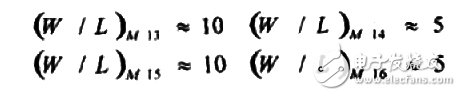

出M13~M15 各管的寬長比為:

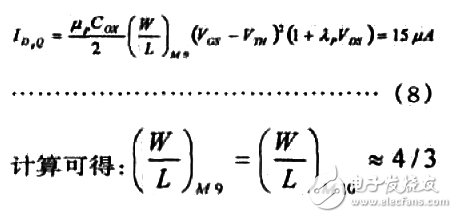

差分對的有源負載管寬長比的計算。從電壓角度出發,為了保證所有的管子在信號范圍內都工作在恒流區或臨界恒流區,而不進入深度線性區,根據總電源電壓VDD =15V,我們可以大致分配M9、M10 的靜態。則:

計算可得:

4.模擬仿真結果分析

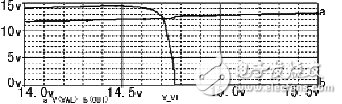

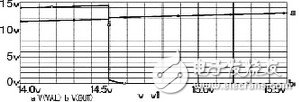

通過上面的計算所得, 利用pspice 對電路進行模擬,在模擬仿真過程中,各管的尺寸有調整,在仿真時,分別增大和減小電源電壓來進行電源掃描,波形見圖2。 從仿真的波形中可以看出:當增大電源電壓時,電壓低于14.78V時,欠壓鎖定;當減小電源電壓時,電壓低于14.5V 時,欠壓鎖定。仍可進一步調整參數,來改善增大電源電壓時的欠壓曲線。

(a)電源掃描的波形(增大電源電壓)

(b)電源掃描的波形(減小電源電壓)

圖2電源掃描的波形圖

5.結論

此欠壓保護電路結構簡單,工藝易實現,可用于功率ic 穩壓電源保護中,當采用不同的工藝時,計算參數的方法相同,也可以采用等比例縮小的原則確定參數。對于一般的欠壓保護,本電路已經足夠。如果對欠壓保護精度和靈敏度要求很高的電路,則可在此電路的基礎上將穩壓輸入部分換成穩壓源,將比較器選用精度更高的比較器,但這樣結構復雜,功耗大,成本高。

評論