基于PCI接口的SpaceWire總線通訊模塊設計

SpaceWire概述

SpaceWire是為更好地滿足星載設備間高速數據傳輸需求而提出的一種高速的(2~400Mbit/s,目前實現的宇航級節點設備之間的速度為200Mbit/s)、點對點、全雙工的串行總線網絡,在2003年1月正式成為歐空局標準。它致力于航天器有效載荷系統數據和控制信息的處理以滿足未來高性能高速數據傳輸為目標,提供了一種統一的用來連接傳感器、數據處理單元、大容量存儲器、遙測子系統以及電地支持設備EGSE(electronic ground support equipment)的基礎架構。

SpaceWire標準具體包括了鏈路、節點和路由三方面的內容。所謂SpaceWire節點,是指傳輸包的流出設備或者流向設備,可以是處理器、存儲單元、傳感器、電地支持設備(EGSE)或連接在SpaceWire總線網絡上的其它單元。

SpaceWire節點通訊板卡硬件設計

EMBC1000-PCISPW是歐比特公司自主研制的完全遵循并實現ECSS-E-ST-50-12C協議規范的航天設備間的高速SpaceWire數據總線的節點終端通訊板卡(本板卡實現了200Mbit/s的速率)。此SpaceWire總線節點通訊板卡可以嵌入在航天子系統中,將航天子系統與其它SpaceWire網絡之間連接,保證航天子系統之間高速、實時、確定、可靠地進行數據交換。其硬件設計分為FPGA控制模塊、PCI接口模塊、MDM9S接口模塊和SRAM緩存模塊。

1.節點通訊卡總體結構

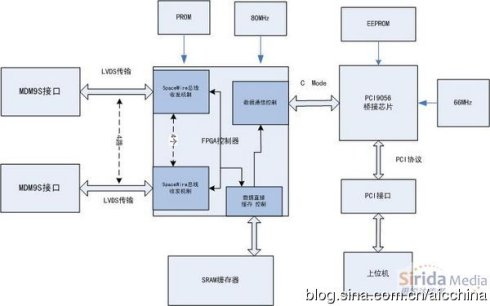

本文設計的SpaceWire總線節點系統硬件架構如圖1所示。各模塊的功能如下:

FPGA控制模塊:實現4路SpaceWire總線通信協議接口功能,硬件實現LVDS信號傳輸,實現數據通訊過程中產生的大量數據實現緩存并與PCI9056通信接口等功能;

SRAM緩存器:存儲SPW總線收發機制中產生的大容量高速數據的緩存功能;

MDM9S接口模塊:MDM9S接口實現FPGA的LVDS信號與外部SPW設備之間的接口功能;

PCI接口模塊:實現PCI總線的接口協議功能,實現FPGA與上位機軟件間進行數據的通信。

2.FPGA控制器

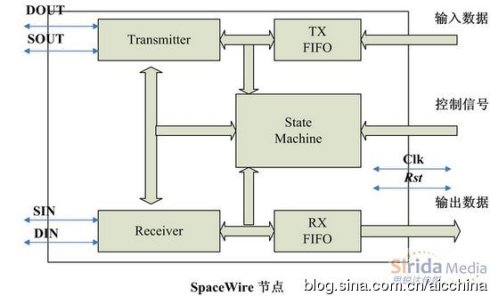

FPGA控制器實現4路SpaceWire總線協議節點控制的全部功能,包括狀態機控制模塊、發送模塊、接收模塊、發生緩存模塊(TXFIFO)、接收緩存模塊(RXFIFO)以及與PCI9056通信接口模塊(PCICTRL)等功能,如圖2所示。

本設計中FPGA采用Altera公司的EP3C55F484I7N芯片,時鐘頻率采用80MHz,同時為了實現SpaceWire總線傳輸速率,FPGA內部采用了PLL對時鐘進行了分頻,以滿足設計要求。

狀態機控制器負責對SPW終端節點的功能控制寄存器、節點狀態寄存器、鏈路地址、時鐘分頻寄存器、直接存儲訪問(DMA)通道控制寄存器等進行參數配置,通過PCI9056地址映射到了上位機的某一段地址空間,因此上位機軟件就可以直接通過對其相關寄存器配置即可完成對SpaceWire節點模塊的控制。下面分發送和接收兩個方面簡單介紹單個SpaceWire總線節點的工作過程:

接收模塊將從MDM9S接口接收到的采用DS(Data-Strobe)方式傳輸的LVDS信號進行數據恢復,并將其傳入到接收緩存中,再傳輸至FPGA內部的雙口RAM中,上位機通過PCI9056橋接芯片的地址映射可以直接讀取該雙口RAM的數據來進行分析處理。發送過程與接收過程類似并相反。

3.PCI9056橋接芯片

在SpaceWire總線節點終端系統與航電計算機系統之間實現PCI通訊有兩個方式,其一就是采用CPLD或者FPGA專門作為一個獨立的模塊實現PCI協議,另外一種方式就是采用專用PCI協議芯片。本終端系統設計中從性能穩定性和結構簡易性方面出發,選擇用PLX公司生產的PCI9056芯片,該芯片可以設置成多種傳輸模式,完成SpaceWire總線節點與航電設備之間的通信橋接功能。

在PCI9056與本地FPGA之間的通信分為直接主模式、直接從模式和DMA模式。由于PCI通信要求達到SpaceWire總線網絡的2Mbit/s至400Mbit/s通訊速率(本板卡實現了200Mbit/s),這里采用的芯片時鐘頻率為66MHz,傳輸模式為直接從模式,PCI9056為主芯片,FPGA為從芯片。

為了與PCI9056進行高效的數據通信,FPGA內部劃出了一部分內存以配置成雙口RAM的形式完成PCI9056對SpaceWire數據的收發以及相應控制寄存器的控制傳輸。

參考文獻:

[1] EMBC1000-PCISPW型SpaceWire節點通訊板卡使用說明書,歐比特控制工程股份有限公司,2013。

[2] 康詠岐, 面向航天應用的SpaceWire節點單元的IP 核設計與實現[J],微電子學與計算機,2005,22(9),120-123。

[3] 陳健飛,曹松,SpaceWire總線接口終端的設計與實現[J],微計算機信息,2010,26(82),123-124。

[4] 陳大羽等,空間高速總線SpaceWire節點的設計與實現[J],航天返回與遙感,2010,31(4),58-64

評論