基于VHDL語言的數字頻率計的設計方案

數字頻率計是通訊設備、計算機、電子產品等生產領域不可缺少的測量儀器。由于硬件設計的器件增加,使設計更加復雜,可靠性變差,延遲增加,測量誤差變大。通過使用EDA技術對系統功能進行描述,運用VHDL語言,使系統簡化,提高整體的性能和可靠性。采用VHDL編程設計的數字頻率計,除了被測信號的整形部分,鍵輸入和數碼顯示以外,其他都在一片FPGA上實現,從而讓整個系統非常精簡,讓其具有靈活的現場更改性,在不改變硬件電路的基礎上,進一步改進提高系統的性能,使數字頻率計具有高速,精確度高,可靠性強,抗干擾等優點,為數字系統進一步的集成創造了條件。

本文引用地址:http://cqxgywz.com/article/201612/333501.htm2.數字頻率計的工作原理

頻率測量方法中,常用的有直接測頻法、倍頻法和等精度測頻法。中直接測頻法是依據頻率的含義把被測頻率信號加到閘門的輸入端,只有在閘門開通時間T(以ls計)內,被測(計數)的脈沖送到十進制計數器進行計數。直接測頻法比其他兩個方案更加簡單方便可行,直接測頻法雖然在低頻段測量時誤差較大,但在低頻段我們可以采用直接測周法加測量,這樣就可以提高測量精度了。直接周期測量法是用被測周期信號直接控制計數門控電路,使主門開放時間等于Tx,時標為Ts的脈沖在主門開放時間進入計數器。設在Tx期間計數值為N,可以根據Tx=N×Ts來算得被測信號周期。因此本文采用低頻測周,高頻測頻的方法來提高精度,減小誤差。

3.主要功能模塊的實現

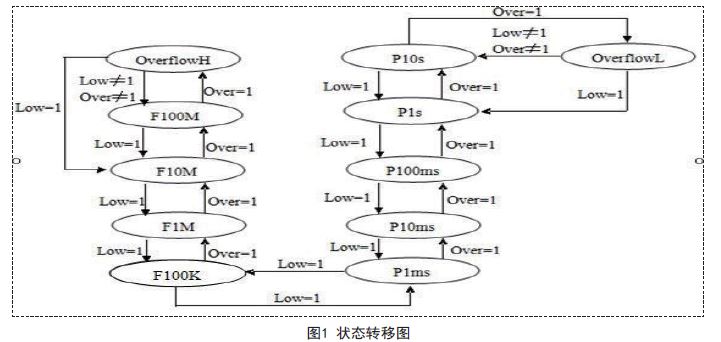

該系統設計的控制器是由狀態機實現,通過在不同測量檔位,選擇合理的時基信號頻率降低誤差,確定各狀態轉移條件和狀態名,采用低頻檔位測周,高頻檔位測頻的方法。20MHz晶振送入分頻器,分出各檔時基信號和其它模塊所需的觸發信號,分頻器將各檔時基信號傳給狀態機,同時待測信號進入狀態機,狀念機進行狀態轉換,將量程溢出信號和狀態顯示信號表征在發光二極管上。如圖表1所示。

3.1 狀態機模塊

首先對系統復位,如果此時狀態機的初始狀態為Fl00k,若超量程信號送入狀態機,則狀態轉換到FlM,如果仍有超量程信號則狀態轉換到F10M,如果仍有超量程信號則狀態轉換到F100M,如果還有超量程信號則狀態轉換到Overflow H產生高溢出信號;若欠量程信號送人狀態機,則狀態轉換到P1ms,如果有超量程信號則狀態轉換到P10ms,如果仍有超量程信號則狀態轉換到P100ms,如果仍有超量程信號則狀態轉換到P 1 s,如果還有超量程則狀態轉換到OverflowL產生低溢出信號。如圖1所示。

3.2 計數器模塊

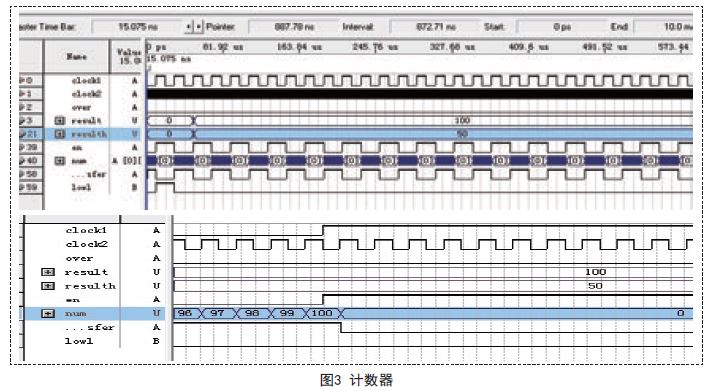

在“待計數信號”的兩個時鐘周期內完成計數與控制信號(Over與Low)的傳輸,在量程合適的情況下,還將計數值輸出。這兩個時鐘周期內,第1個時鐘周期完成計數,第2個時鐘周期完成控制信號的傳輸與計數值輸出。這樣做的好處是穩定,將計數與控制信號傳輸分開進行。避免了一些可能遇到的“時鐘跳變”.但這種做法的缺點也很明顯,那就是在測周期模式下,假如待測信號是1Hz的,那么系統可能需要2s(兩個時鐘周期)才能顯示正確的數值。

3.3 十分頻模塊

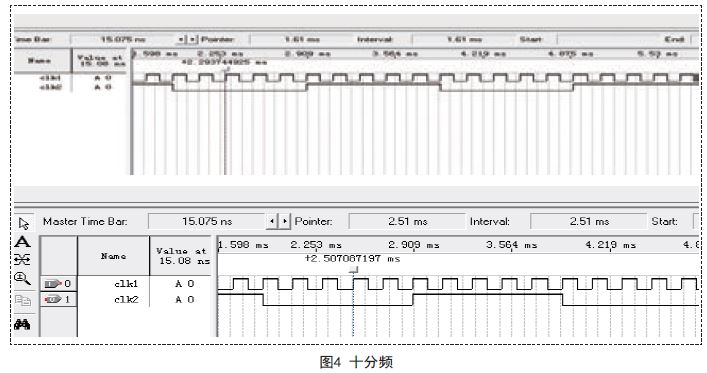

由于1kHz~10kHz的信號無論用測頻法還是測周期法都是不可行的,可以采用預分頻的方法,將1kHz~10kHz的信號十分頻,然后用測周期法測出周期,再計算出頻率。

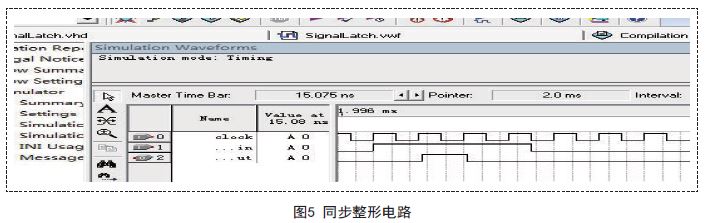

3.4 同步整形電路模塊

通過同步整形電路處理外部的異步信號,超量程和欠量程。源程序如下:

library ieee;use ieee.std_logic_1164.all;entity SignalLatch is4.系統的功能仿真和驗證分析。

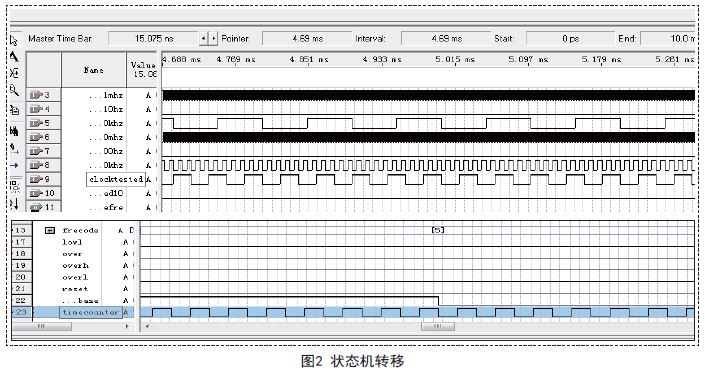

據狀態轉換圖,這里將狀態機的程序分成兩個進程,進程1完成狀態轉移過程,進程2控制各狀態下的輸出值如下圖2所示,timecounter=clocktested為50KHz.

為了方便觀察,將數值改小,計數值大于100且小于或等于1000時輸出!將clock1設為50K,clock2計數時鐘設為5M,得出仿真如圖3所示Result為100符合計數要求。

如圖4所示給clk1一個5KHz的頻率,經過十分頻后clk2輸出0.5KHz,clk1的周期是0.2ms,經過十分頻后是2ms

同步整形電路仿真如圖5所示。

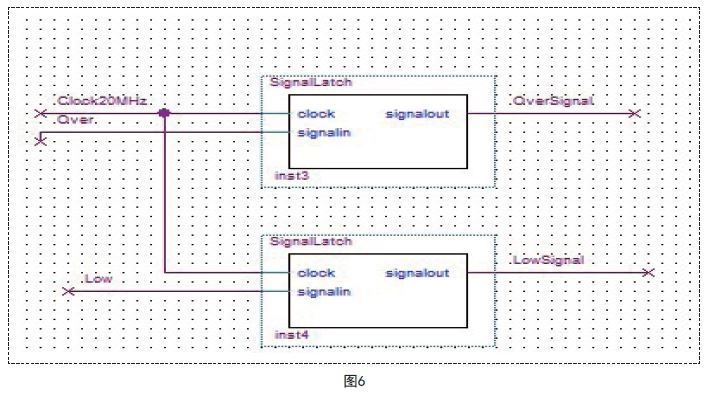

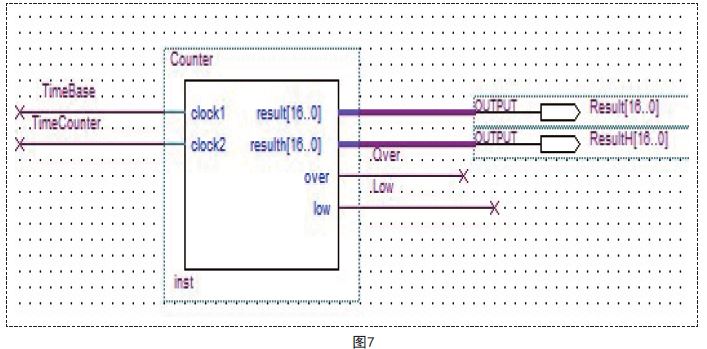

由以上模塊進行仿真得出了頻率的測量。如圖6、7、8所示。

5.結論

本方案所設計的數字頻率計占用FPGA芯片資源較少,成本較低,減少了電路的尺寸,具有一定的實用價值。利用QuartusII平臺進行了仿真和硬件測試,基本達到了設計的要求。從而證實了本方案的具有較好可靠性,靈活性以及實用性

評論