CPRI協議分析儀的硬件開發與實現

隨著通信技術的發展,標準化的基帶-射頻接口越來越受到各廠家的關注,在近幾年內相繼出現了CPRI、OBSAI、TDRI接口標準。CPRI作為通用開放接口標準,由于其實現上的經濟簡便性受到了多方廠家的支持,設備供應商相繼推出了基于CRPI協議標準的拉遠產品,另一方面基于CRPI協議的交換機和路由器也在逐漸的成熟和推廣。開放的通用接口為3G基站產品節約成本、提高通用性和靈活性提供了方便。

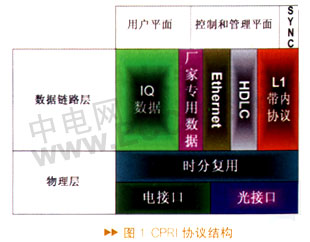

本文引用地址:http://cqxgywz.com/article/201701/337676.htmCPRI協議由愛立信、華為、NEC、北電和西門子五個廠家聯合發起制定,用于無線通訊基站中基帶到射頻之間的通用接口協議,對其它組織和廠家開放。CPRI大部分內容主要針對WCDMA標準,為其可實現良好服務。經分析,CPRI協議同樣適用于TD-SCDMA第三代移動通訊標準。CPRI協議橫向分為物理層和數據鏈路層;縱向分為用戶平面、控制管理平面和同步平面,具有圖1所示的結構。

|

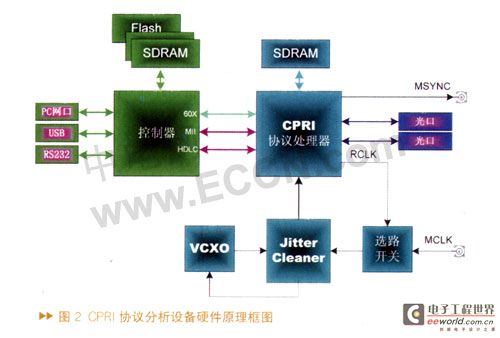

CPRI協議分析儀主要實現射頻單元、基帶單元的功能模擬。一方面采集數據進行協議分析,另一方面則產生模擬數據進行協議發送。基于圖1的協議結構,分析儀由控制器、CPRI協議處理器、時鐘處理以及對外接口四個主要功能單元構成,支持614.4Mbps、1.2288Gbps和2.4576Gbps三種數據速率,原理框圖如圖2示。

|

差分信號的端接和匹配

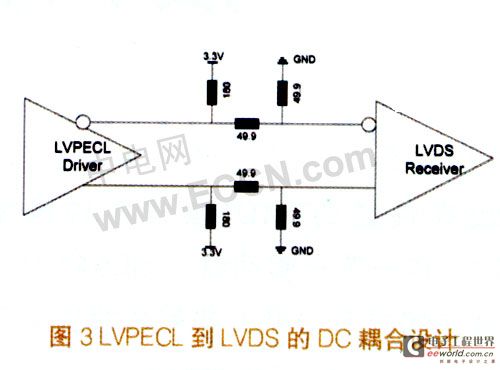

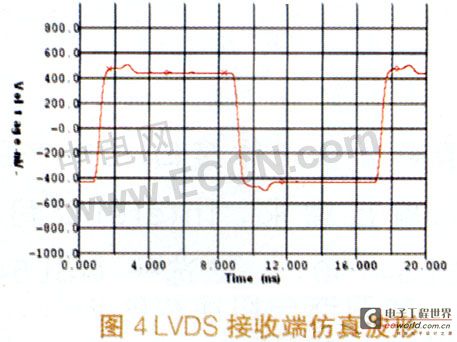

CPRI分析儀板卡上存在LVDS、CML和LVPECL等多種差分電平,不同電平之間的互連需要精心地設計他們之間的匹配和端接,以實現穩定可靠的工作。LVPECL到LVDS之間采用DC耦合,圖3和圖4顯示了61.44MHz時鐘在這種設計下的參數和仿真結果。

|

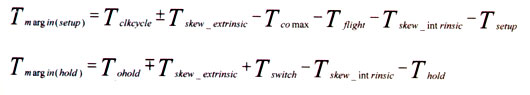

所有的同步時序單沿采樣分析建立在如下兩個時序閉環公式的基礎上:

公式:

公式中各參數的含義及其來源可參考下表:

|

評論