信號完整性分析基礎系列之十九--高速串行信號接收機測試

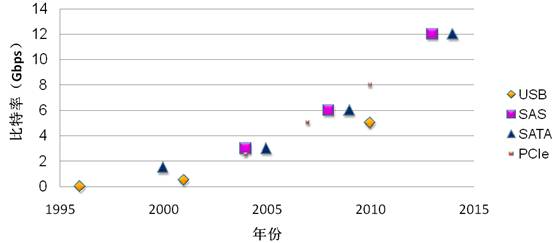

網絡、多媒體、移動通信對提高數據吞吐率的需求與日俱增,推動計算機和通信技術不斷突破速度極限。圖1是當前主流計算機外設總線的速率演變情況。

圖1主流高速串行標準演進圖

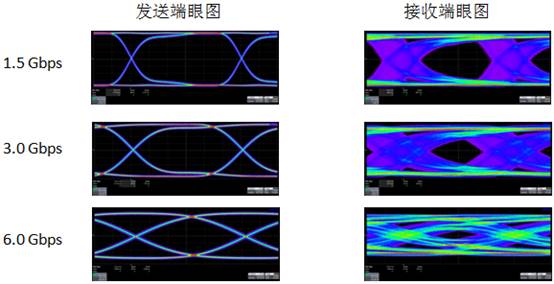

數據率越高,信道趨膚效應和介質損耗對信號質量的影響越嚴重,在時域上表現為:邊沿變緩,碼間干擾加劇,抖動增加。通常使用眼圖來評估高速信號質量。下圖是三種速率的信號在發送端和接收端分別測得的眼圖。可以明顯看出,速率越高,接收端的眼圖閉合程度越小。能否在接收端正確檢測出受損的信號,是高速收發器芯片設計者面臨的挑戰。

圖2不同速率信號的失真程度

在以往的高速串行信號一致性測試標準里,一般都要求測試發送端性能,比如輸出電壓擺幅、上升時間、抖動、眼圖等。隨著速率提高,僅僅測試信號發送端已經不能保證高速鏈路能按預期性能正常工作,必須對接收機性能也進行測試。USB 3.0、PCI Express 3.0以及SATA和SAS規范已經明確要求進行接收機測試。

2.接收機測試原理

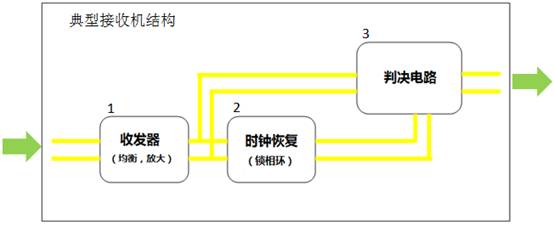

在發送器測試中,通常利用示波器直接測量輸出信號的幅度、上升/下降時間、眼圖和抖動,從而評估發送器的驅動能力、預加重、參考時鐘穩定性等各項性能。在接收端,典型的接收機芯片框圖如下:

圖3典型接收機內部框圖

它包含

信號檢測(放大,均衡)

基于鎖相環(PLL)的時鐘恢復

判決電路(并轉串,線路碼解碼)

對接收機性能的測試實際就是對以上三個主要部件的性能測試:

1)可以識別出多小幅度的信號,即接收靈敏度

2)時鐘恢復電路中的鎖相環能否去除低頻抖動

3)能夠正確識別出帶有多大抖動的數據,即抖動容限

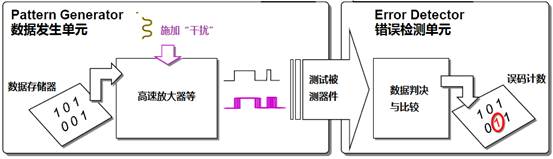

不像發送端可以直接測量被測件(Device Under Test,DUT)輸出的信號,信號進入接收機內部后無法直接觀測,一般使用儀器產生一定樣本量、一定特征的激勵數據流給DUT。這些特征一般是多種形式的“干擾”,儀器通過施加不同程度的“干擾”,測試接收機的表現。

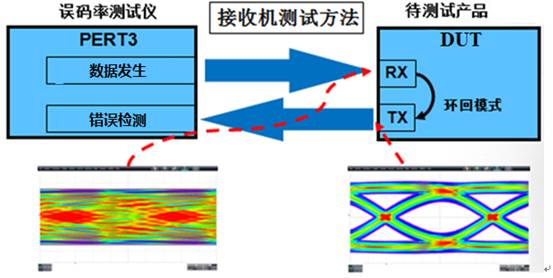

這種儀器一般是誤碼率測試儀(Bit Error Rate Tester,BERT)。簡單的說,誤碼率測試就是發送已知數據給被測接收機芯片,通過量化被錯誤判決數據的比例來衡量接收機芯片的性能。在功能上,誤碼率測試儀包括數據發生(Pattern Gernerter)和錯誤檢測(Error Detetor)兩個部分,即前者產生激勵,后者檢測響應。

圖4誤碼率測試儀工作原理框圖

測試時,誤碼率測試儀和DUT收發互連形成回環,如圖5。Pattern Generator發出帶有“干擾”的信號給DUT。DUT將接收到的數據經過內部回環又發送回給誤碼率測試儀。一般經過DUT內部的檢測和時鐘域變換,發送回去的數據不再帶有“干擾”。

圖5誤碼率測試儀與DUT回環連接

DUT一般有兩種回環模式:

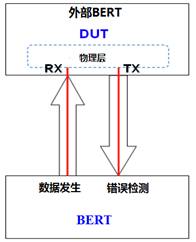

1)外部BERT(或稱Retimed Loopback)

圖6外部BERT測試框圖

DUT將RX端收到的BERT數據從TX端發送回去,由BERT對比發送和接收到的數據

評論