胡為東系列文章之三--高速串行信號的接收端測試

1、最簡單的接收端結構

|

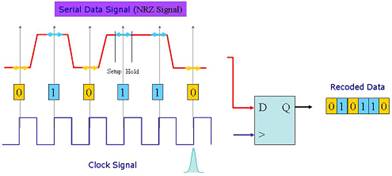

圖1基本D觸發器的鎖存數據示意圖

最簡單的接收端可以看著一個D觸發器,有一個時鐘輸入接口和一個信號輸入接口及一個信號輸出接口。輸入時鐘對D觸發器和輸入數據進行觸發和采樣后輸出數據。如上圖1所示為一個基本的D觸發器鎖存串行數據基本示意圖。

一般低速信號接收端的結構和工作原理相對來說比較簡單。且傳輸的信號速率也往往很低,信號即使經過較長的通道傳輸后也不會有太大的衰減,因此接收端出現問題的概率會小很多,所以一般5Gbps速率以下的信號的規范通常不會將接收端測試作為必選的測試項目。

2、典型高速串行數據的基本結構

圖2典型的并行/串行數據的基本傳輸結構

并行數據轉換成串行數據并輔以相應的編碼,可以以LVDS或者CML等差分電平的方式實現高速、高可靠的傳輸,傳輸通道結構也可實現極大的簡化。從上述結構圖中我們可以看出,串行數據傳輸鏈路中是沒有專門的時鐘信號傳輸的,那么接收端如何實現對串行數據的解串、解碼呢?事實上接收端會有專門的CDR(Clock Data Recovery)電路用以從串行數據中恢復出時鐘。因此,一個最典型的串行數據鏈路的發送端的內部結構至少應包括:串行化(Serializer)電路、8B/10B編碼電路(通常在8B/10B編碼電路之前還有一級Scramble編碼電路以減小信號的高頻諧波分量及信號失真);接收端應至少包括解串電路(Deserializer)、8B/10B解碼電路、CDR時鐘數據恢復電路等。

當串行數據的速率進一步提高,比如說數據速率達到5Gbps以上,如USB3.0,PCIE GEN3等,串行數據鏈路中各個組成成分都會影響到信號的質量。如傳輸線、接插件、阻抗不連續、芯片封裝等,在實際應用中我們常會發現在接收端芯片管腳處測試得到的信號眼圖已經接近閉合,眼圖閉合的主要原因來自于高速信號傳輸過程中受到傳輸鏈路各組成成分的影響而導致的。為了改善信號眼圖的質量,芯片端會采用一些補償的措施,如在發送端采取預加重的方法對信號的幅度和邊沿提前進行優化,來補償高速信號通過傳輸鏈路后可能帶來的損耗;而在接收端芯片中還可以使用均衡的方法來實現對信號的補償。這樣接收端和發送端的結構會變得更為復雜。如下圖3所示,接收端有均衡器、時鐘數據恢復電路、解串電路、8B/10B解碼、Scramble解碼、彈性緩沖器(Elastic Buffer,通過插入或者丟掉時鐘對齊符號碼來實現發送端和接收端的時鐘速率的一致)等。

評論