詳解數字通訊的2M測試系統

數字通訊飛速發展的今天, 2M口日益成為重要的設備投入業務測試點和運營維護測試點。數字通訊飛速發展的今天,建立綜合業務數字網正成為電信經營者努力的方向。差錯(誤碼、誤塊)性能作為數字網的重要傳輸性能指標,是網絡營運者進行數字網建設、維護的重要依據;也是評估電信業務性能優劣的標準之一。 因此,國際電聯(ITU-T)極為重視對差錯的研究,近年來,針對數字網的設計、安裝、維護的要求,推出了一系列有關誤碼性能的建議。目前我國工程技術人員所使用的測試儀多為國外進口產品,產品價格昂貴。而國產的測試儀功能相對簡單。為此我們研究設計了一款基于ARM的2M傳輸口測試系統。2Mb/s是我國數字時分復用基群2048kbit/s 的簡稱,是PCM傳輸與交換的基礎。本文涉及的2M傳輸口測試系統為手持式PCM 2M綜合測試儀器。

2系統硬件設計

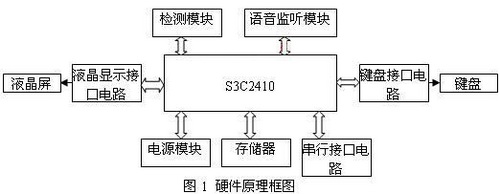

根據2M測試系統的性能要求,硬件層主要由系統核心部分、檢測模塊部分和語音監聽部分組成。硬件原理框圖如圖1。

2.1 系統核心組成設計

在此系統中我們選用三星公司的S3C2410[1]微控制器芯片,內含一個由ARM公司設計的16/32位ARM920T RISC處理器核,ARM920T為低功耗、高性能的16/32核。S3C2410微控制器芯片在本系統中的主要作用是:(1)讀寫和控制各模塊芯片;(2)讀取鍵值;(3)控制液晶屏的顯示;(4)在測量時進行數據的讀取和處理;(5)對存儲器進行讀寫;(6)通過串行口與微機進行通訊,將測試結果上傳微機。存儲器以HY29LV160 FLASH作為程序存儲器,以HY57V641620SDRAM作內存,構成嵌入式系統核心。S3C2410芯片內含一個IIC總線控制器,可方便的與各種帶有IIC接口的器件相連。在該系統中,外擴一片AT24C01作為IIC存儲器。可存放在系統掉電時需要保存的數據。

2.2 檢測模塊部分的設計

檢測模塊部分由芯片DS21354[2]和芯片DS21372組成,這兩塊芯片協同工作共同完成檢測功能。DS21354芯片主要完成發送和接收2048kbit/s 的PCM 信號,并從中檢測誤碼和告警狀態。DS21372是一種軟件可編程的測試圖樣產生、接收、分析器,能適用于對差錯性能要求最嚴格的數字傳輸設備的能力。具有兩種測試圖樣的生成方式(偽隨機序列和重復序列)。符合CCITT/ITU O.151,O.152,O.153和 O.161標準。DS2172 可以工作在直流到20MHz,這樣寬的頻率工作范圍使它可以靈活地使用在現有的設備和處于測試階段的新設備中,如:傳輸設備,交換設備,復用器,DAC,路由器,橋設備等。

DS21372[3]中包含有4個功能塊:圖樣產生,圖樣檢測,差錯計數和控制接口,具有完全獨立的傳輸和接收部分,8bit的并行處理器接口,可以編程產生最大長度為(232-1)bits的偽隨機序列圖樣,可編程的多項式長度和反饋量可以用于任意偽隨機序列圖樣的生成,包括:26-1、29-1、211-1、215-1、220-1、223-1和232-1。或者用戶編程的自定義長度從1到32bits的重復序列圖樣。擁有32bit差錯計數器和比特計數器。軟件編程的比特差錯插入,最大比特差錯率圖樣的檢測可達10-2。DS21372能向線路插入單個bit或從10-1bit到10-7bit誤碼率的誤碼,以檢驗設備的操作狀態和連通性。用于分析、評測、解決數字通信系統中出現的問題。

2.3 語音監聽模塊部分的設計

語音監聽部分采用時隙交換電路和語音檢測模塊組成,語音檢測模塊采用ZARLINK的3.3V多功能CODECMT91L60[4]。這款芯片能實現聲音信號的A/D、D/A轉換,并為標準的電話機手柄等接收發送裝置提供模擬接口。當E1接口電路與2M實際線路連通后,2M 鏈路上的話音時隙要通過時隙交換電路與MT91L60電路相連,構成了話音時隙收發的通道。在這個過程中要初始化時隙交換電路,將2M鏈路上的需要監測的話音時隙交換至MT91L60。打開MT91L60接收通路至電話機手柄輸出,設置ITU-T A-law話音編碼方式,設置接收增益+6dB,設置非消側音非環回模式等。這些設置是通過設置MT91L60內部寄存器完成的,完成這一系列設置后,語音測試就可以開始了,語音可以通過電話機手柄聽到,其他測試內容可以從MT91L60內部寄存器讀到結果。

3系統軟件設計

軟件部分主要由啟動代碼的設計和應用程序的設計,基于ARM是復雜的片上系統(SOC),這種復雜系統里的多數硬件模塊都是可配置的,需要由軟件來設置其需要的工作狀態。因此在用戶的應用程序啟動之前,需要有專門的一段啟動代碼來完成對系統的初始化。由于這類代碼直接面對處理器內核和硬件控制器進行編程,一般都是用匯編語言寫的。啟動代碼就是完成各種初始化工作,并引導進入C程序。

3.1 bootloader設計

啟動代碼[5]的主要實現功能包括以下部分:

(1)設置程序入口指針;

(2)設置中斷向量表;

(3)初始化存儲器系統;

(4)初始化CPU各種模式的堆棧和寄存器;

(5)初始化目標系統中要使用的各種片內外設;

(6)初始化用戶程序執行環境;

(7)引導主應用程

具體實現的部分代碼如下:

AERA Init, CODE,READONLY

ENTRY ;定義入口點

B SYS_RST_HANDLER ;系統上電復位操作

B UDF_INS_HANDLER ;處理未定義中斷模式

B SWI_SVC_HANDLER ;處理軟件中斷

B INS_ABT_HANDLER

B DAT_ABT_HANDLER ;處理中止異常

B .

BIRQ_SVC_HANDLER ;處理IRQ 中斷

B FIQ_SVC_HANDLER ;處理FIQ中斷

SYS_RST_HANDLER

MSR R0, CPSR ;禁止中斷

ORR R0,R0,#0XC0

MSR CPSR_C,R0

BL initcpu ;調整PLL和時鐘

BL initmem ;初始化存儲器

BL initstack ;設置堆棧

… …

… …

… …

B main ; 跳轉到主應用程序

3.2應用程序的設計

應用程序采用C語言編寫,由其實現本系統中所需的各種功能。根據系統功能需求,軟件劃分為以下模塊:液晶顯示模塊、測試設置模塊、測試指標計算模塊等部分。軟件設計思想是利用S3C2410的中斷控制整個軟件的流程。共使用4個硬件中斷來完成系統的功能:一個內部硬件定時中斷,3個外部硬件中斷(鍵盤中斷、串口中斷、E1測試中斷)。主程序流程圖如圖2所示。

評論