如何解決以太網故障?

以太網頻繁出現通信異常、丟包等現象,是否會想到是硬件電路設計問題?成熟的以太網電路設計看似簡單,但如何保證通信質量,在通信異常時如何快速定位問題,本文將通過實際案例來講述網絡通訊異常的解析過程和處理方案。

本文引用地址:http://cqxgywz.com/article/201807/389277.htm一、案例情況

一日,核心板基于TI公司的DP83848KSQ PHY芯片二次開發時搭建一路百兆以太網電路,在研發測試階段,發現以太網電路頻繁出現通信異常,表現為工作一段時間后網絡自動掉線,無法重連。多臺樣機均表現出同樣的現象,于是研發展開一系列的問題定位。

二、現場排查

軟硬件工程師開始各自的問題定位,這里則談談硬件問題定位。

1.電源電路測試

首先先確定電源電路情況,測試PHY芯片工作時和通信異常時的供電電源的電壓,電源電壓穩定,無跌落,電平為3.3V;其次測試紋波噪聲,測試結果也滿足要求。電源電路影響暫可以排除。

2.原理圖檢查:

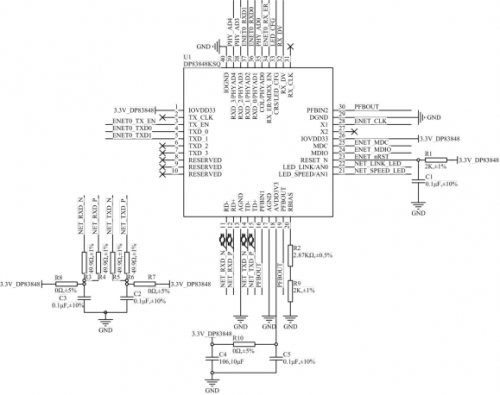

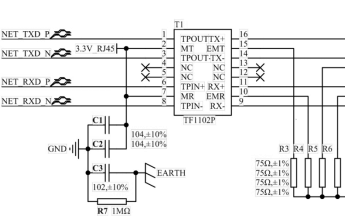

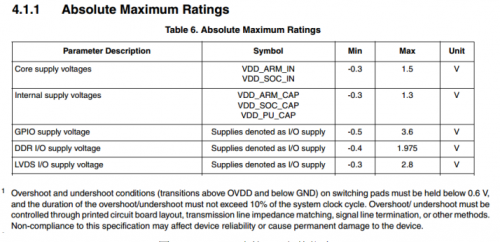

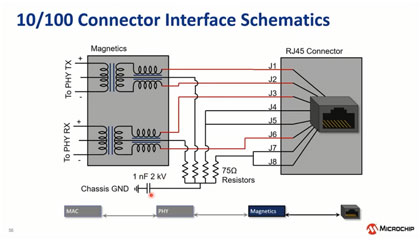

然后從原理圖下手,檢查PHY芯片的外圍電路和對照處理器的引腳順序,如圖1所示,外圍電路接線無誤,設計符合設計規范。繼續檢查以太網的變壓器電路,如圖2所示,該電路也符合設計規范。原理圖設計基本可以排除。

圖1 PHY芯片外圍電路圖

圖2 變壓器外圍電路圖

3.樣機電路測試

時鐘信號測試:時鐘信號幅值、頻率、上升下降時間、占空比等參數均滿足要求。

時序測試:數據信號和控制信號的時序裕量均滿足手冊要求。

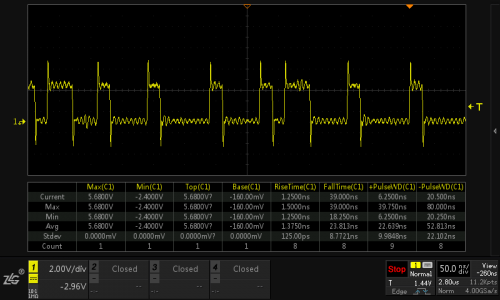

數據信號波形測試:在信號測試時,發現PHY芯片的數據信號和控制信號有異常的波形,如下圖3、4所示:

圖3 RMII_RXD信號

圖4 RMII_TXD信號

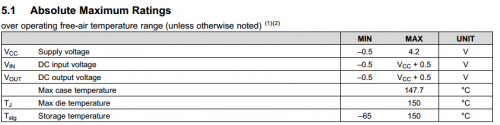

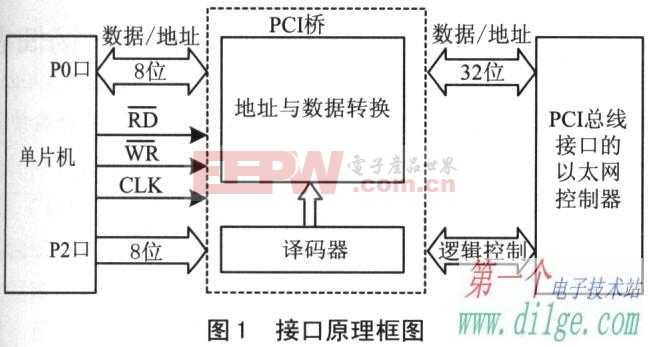

圖5 PHY芯片的IO參數信息

圖6 處理器芯片的IO參數信息

評論