高云半導體發布基于小蜜蜂家族GW1NS系列GW1NS-2 FPGA-SoC芯片的軟硬件設計一體化開發平臺

中國廣州,2018年7月23日,廣東高云半導體科技股份有限公司(以下簡稱“高云半導體”)今日宣布:高云半導體發布基于小蜜蜂家族GW1NS系列GW1NS-2 FPGA-SoC芯片的軟硬件設計一體化開發平臺。

本文引用地址:http://cqxgywz.com/article/201807/389337.htm高云半導體軟硬件設計一體化開發平臺,是基于GW1NS-2 FPGA-SoC 所提供的多種固定或可配置的設備模型庫以及與設備相匹配的軟件驅動器庫,使硬件設計工具與軟件設計工具相結合,從而支持GW1NS-2 FPGA-SoC的硬件架構設計和內嵌微處理器的軟件編譯/并接/查錯(Compile、Link、In-Circuit-Emulation/Debug)等功能;并支持ARM-MDK 與GNU兩套軟件設計工具。

與傳統FPGA只包含可編程邏輯單元不同,高云半導體GW1NS-2作為一款真正微型化的FPGA-SoC系統芯片,除可編程邏輯單元之外,其內嵌了ARM Cortex-M3微處理器,以及作為微處理器固定外設的儲存器Block-RAM、閃存FLASH、ADC及USB-2.0 PHY,因而,GW1NS-2 FPGA-SoC系統芯片的應用設計兼具軟、硬件設計流程。

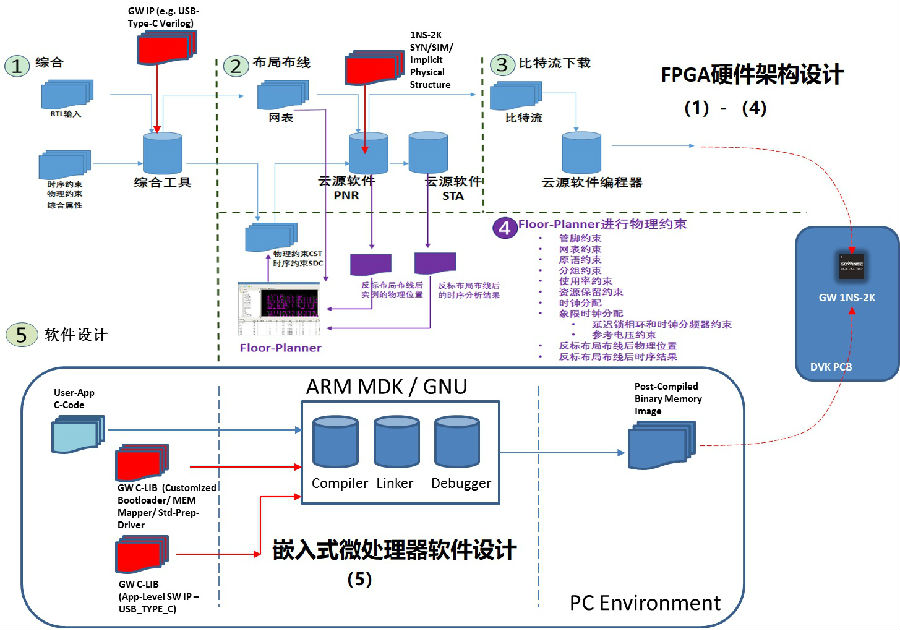

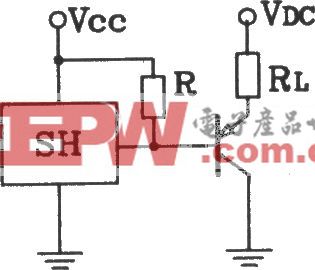

通過高云半導體提供的軟硬件設計一體化開發平臺,GW1NS-2應用設計的FPGA構架硬件設計與嵌入式微處理器軟件設計,兩者有機無縫的結合在一起,具體如圖1所示,從而能夠大幅提高用戶設計的效率。

圖1 GW1NS-2 FPGA-SoC的應用設計結合軟硬件設計流程

所謂FPGA-SoC系統,即是利用FPGA可編程的優勢,將用戶在不同應用場景所需要的非固定接口與外設,由只需要1.7KLUT邏輯內的低密度FPGA可編程邏輯單元來編程實現,配置成特定內嵌CPU的設備,直接將CPU數據處理功能結合入微型化低密度FPGA,極大地拓展了FPGA芯片系統化應用的深度和廣度。

FPGA構架硬件設計從電路RTL(Verilog或VHDL)開始,經邏輯綜合工具成電路網表,然后配置上電路設計的物理約束與時序約束,再經高云云源軟件布局布線,通過靜態時序分析和電路設計布局往復調整之后,成為硬件二進制比特流文檔,最后經云源軟件編程器下載入GW1NS-2 FPGA-SoC 進行硬件的編程。

FPGA-SoC的設計目的是將GW1NS-2內嵌的FPGA配置成內嵌微處理器(CPU)的物理設備。嵌入式微處理器軟件設計可從安裝在個人電腦(PC)上的軟件設計工具(Compiler、Linker、Debugger)開始,編寫C語言軟件程序,然后編譯成軟件二進制文檔,經軟件設計工具下載入連接嵌入式微處理器的儲存器之中。器件上電后,嵌入式微處理器會自動從儲存器當中讀出并執行軟件程序,按軟件程序命令調用內嵌FPGA內已配置好的物理設備以及嵌入式微處理器附帶固定物理設備,并處理數據,完成電路軟硬件設計功能。

“高云半導體提供面向市場自主研發的新一代 FPGA 硬件開發環境,支持GW1NS系列FPGA 產品,”高云半導體首席技術官宋寧博士說道,“能夠完成FPGA綜合、布局、布線、產生數據流文件及下載等一站式工作。”

“高云半導體 GW1NS-2 FPGA-SoC芯片的軟硬件設計一體化開發平臺,就是在新一代 FPGA 硬件開發環境的基礎上,有機無縫地接入嵌入式微處理器軟件設計流程, 使之成為一個一站式的整體設計平臺”,高云半導體軟核研發部門負責人高級經理高彤軍先生介紹,“從而縮短顧客從概念到成品的過程,最大化,最優化地發揮基于GW1NS-2微型FPGA-SoC所設計的顧客應用產品之優勝特性”。

評論