移位寄存器串入并出與并入串出

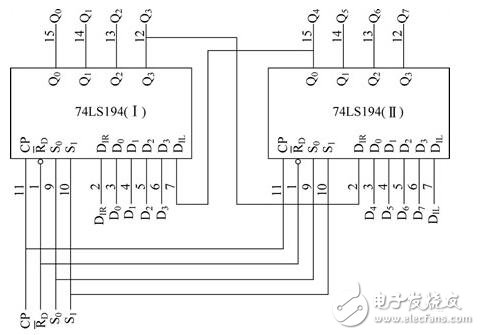

在數字電路中,移位寄存器(英語:shift register)是一種在若干相同時間脈沖下工作的觸發器為基礎的器件,數據以并行或串行的方式輸入到該器件中,然后每個時間脈沖依次向左或右移動一個比特,在輸出端進行輸出。這種移位寄存器是一維的,事實上還有多維的移位寄存器,即輸入、輸出的數據本身就是一些列位。實現這種多維移位寄存器的方法可以是將幾個具有相同位數的移位寄存器并聯起來。

本文引用地址:http://cqxgywz.com/article/201907/402735.htm移位寄存器的輸入、輸出都可以是并行或串行的。它們經常被配置成串入并出(serial-in, parallel-out, SIPO)的形式或并入串出(parallel-in, serial-out, PISO),這樣就可以實現并行數據和串行數據的轉換。當然,也有輸入、輸出同時為串行或并行的情況。此外,還有一些移位寄存器為雙向的,也就是說它允許數據來回傳輸,輸入端同時可以作為輸出端,輸出端同時也可以作為輸入端。如果把移位寄存器的串行輸入端,和并行輸出端的最后一位連接起來,還可以構成循環移位寄存器(circular shift register),用來實現循環計數功能。

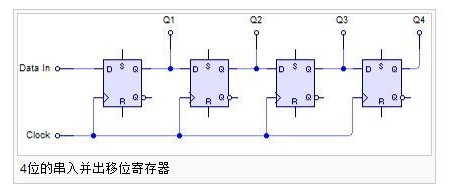

串入并出

串入并出形式的移位寄存器接法,可以將輸入的串行數據以并行格式輸出。串行通信要求的幾位數據完成輸入之后,就可以在輸出端的各位同時讀出并行數據。

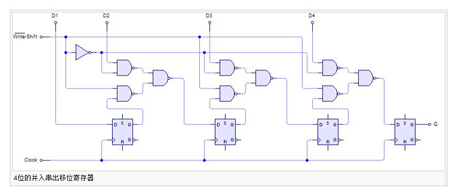

并入串出

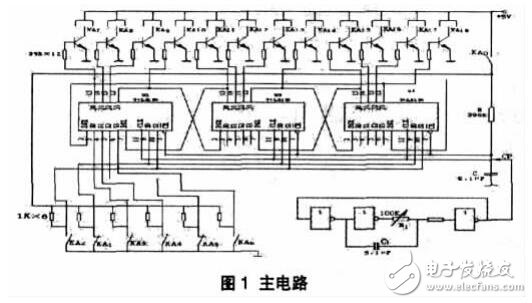

并入串出形式的移位寄存器接法,通過下圖所示D1-D4并行輸入段接收4位外部并行數據,而Q為串行輸出的引腳。為了將數據寫入到寄存器中,寫/移位控制線必須保持低電平。寫入完成,需要移位時,寫/移位控制線則必須處于高電平,而且必須給予時間脈沖,每提供一個時間脈沖,向左(或向右)移動一位。

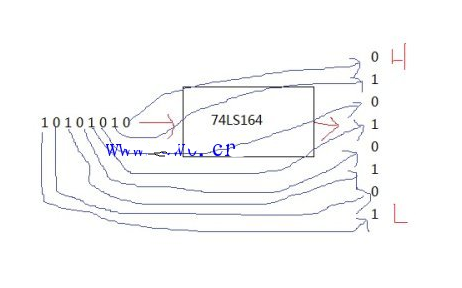

串入并出移位寄存器開發經驗

對于串入并出移位寄存器以下是我個人的理解和實際開發工程中得出的經驗:

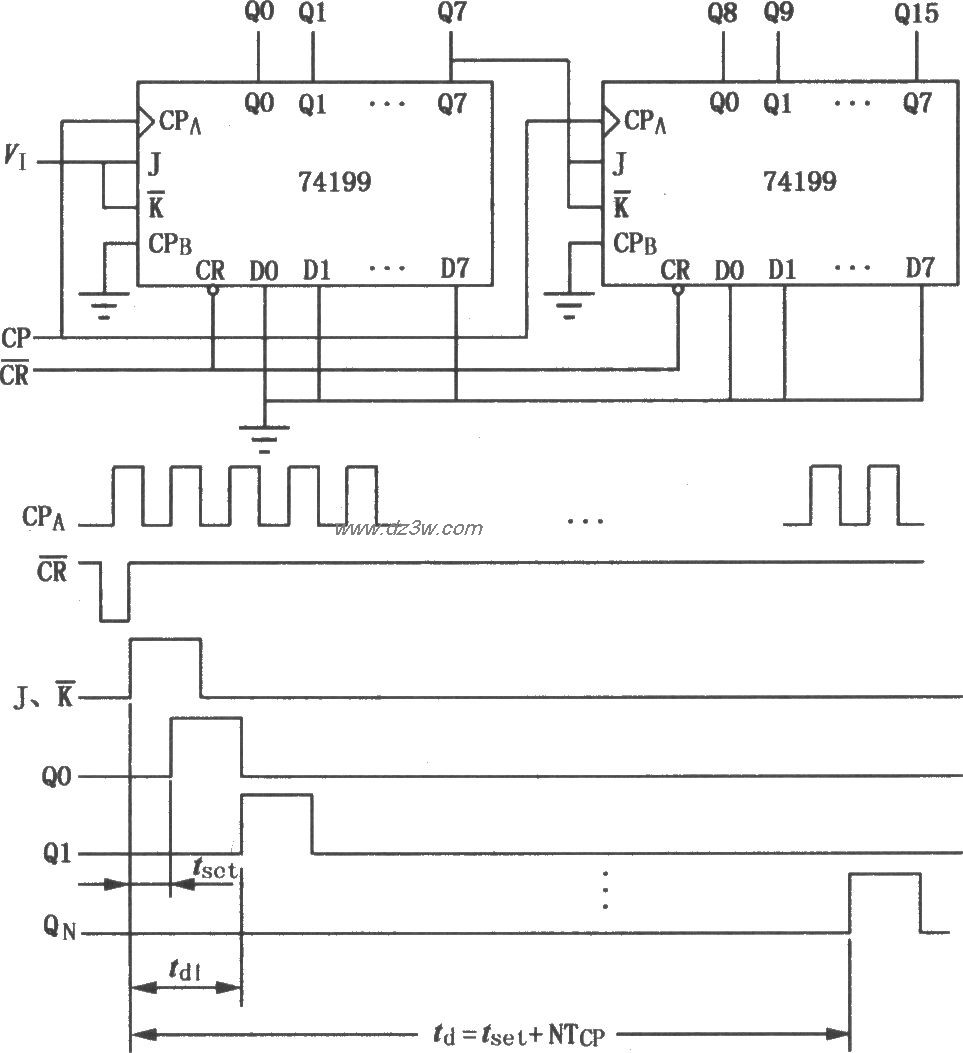

由我上圖所畫,可以得出,一個8位串入數據輸入, 8位并行輸出。可以看出先移的是高位,就是第一個位進去的到最后會在最高位。

移位寄存器串入并出與并入串出

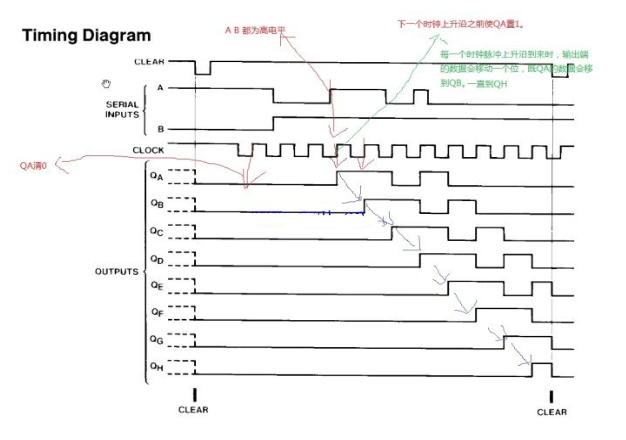

上圖為時序圖,A、B是輸入。

clean是清0端,低電平有效。就是如果給個低電平那么輸出都為0,強制都輸出0。一般接高電平。

clock是時鐘,上升沿有效。

由上圖可以得出如果A、B有一個為低電平,那么阻止新數據的進入,并在下一個時鐘上升沿時,將QA端清0。

如果A、B端都為高電平則會使能信號輸入,并在下一個時鐘脈沖的上升沿之前使輸出端QA 置1。每一個時鐘脈沖上升沿到來時,輸出端的數據會移動一個位,既QA的數據會移動到QB,一直到QH。

評論