STM32+A3P125 圖形控制器方案,多參數監護儀數據采集模塊深度解析

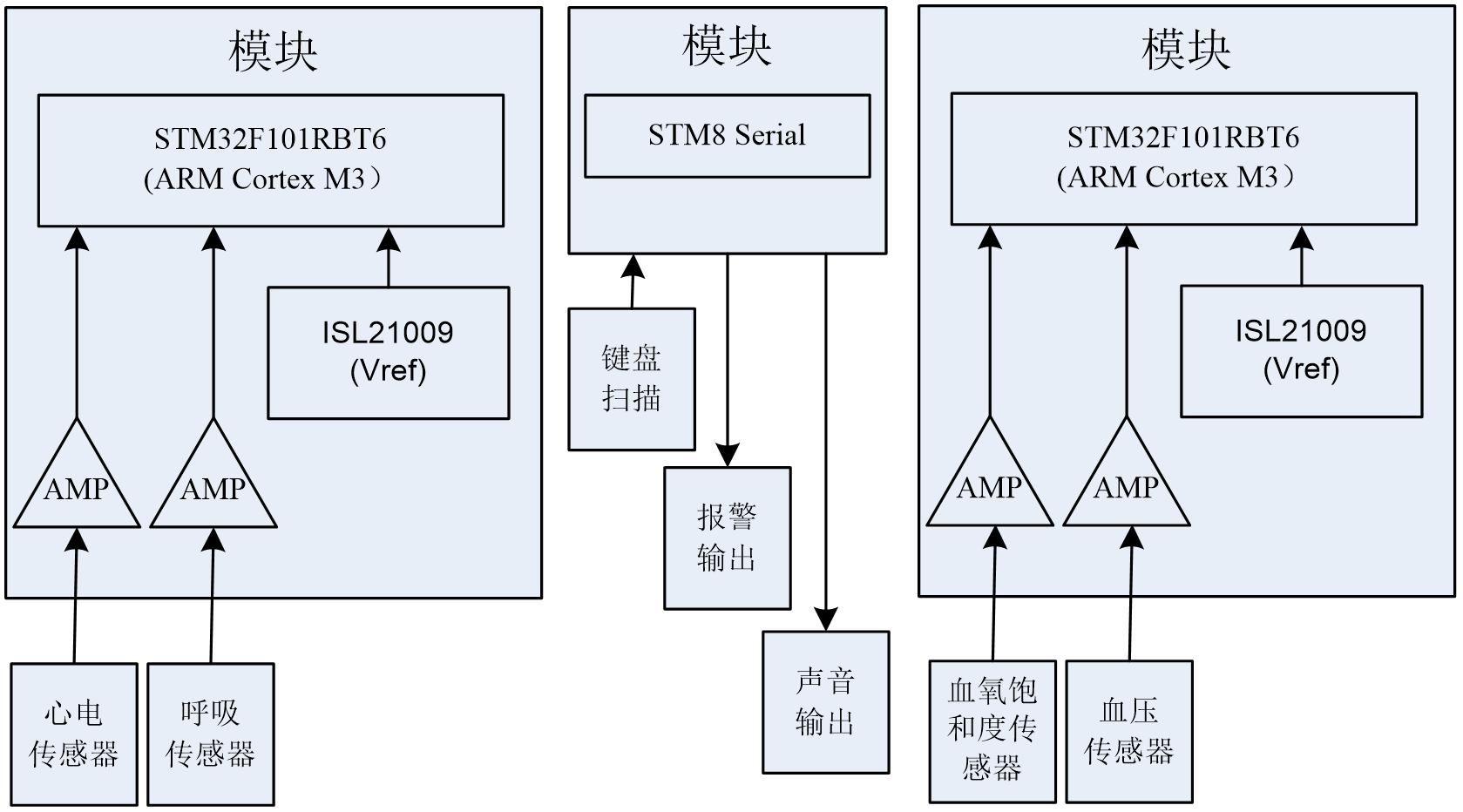

一、生理信號采集與轉換架構

多參數監護儀數據采集模塊是將人體生理信號轉化為數字信號的核心單元,其架構遵循 “傳感器感知→信號調理→模數轉換→數字處理” 的標準化流程:

1. 傳感器類型與生理信號轉換

傳感器類型 | 生理信號 | 轉換原理 | 典型芯片 / 方案 |

ECG 電極陣列 | 心臟電活動 | 體表電位差采集 | 10 電極組合(VR/VL/VF 等)+ INA128 儀表放大器 |

SpO2 指夾探頭 | 血氧飽和度 | 660nm 紅光 / 940nm 近紅外光吸收 | 雙波長 LED + 光電二極管(如 APDS-9008) |

NIBP 袖帶 | 無創血壓 | 振蕩法測量袖帶壓力波動 | MPX5050 壓力傳感器 + 氣泵控制電路 |

熱敏電阻 | 體溫 | 電阻值隨溫度變化(如 PT1000) | NTC 熱敏電阻 + 恒流源電路 |

有創血壓探頭 | 有創血壓(IBP) | 導管內壓力轉換為電壓信號 | 壓阻式壓力傳感器(如 MS5421) |

呼吸阻抗電極 | 呼吸頻率(RESP) | 胸壁電阻抗變化(4~30kHz 激勵電流) | 恒流源 + 儀表運放(如 IS |

二、硬件架構與系統定位

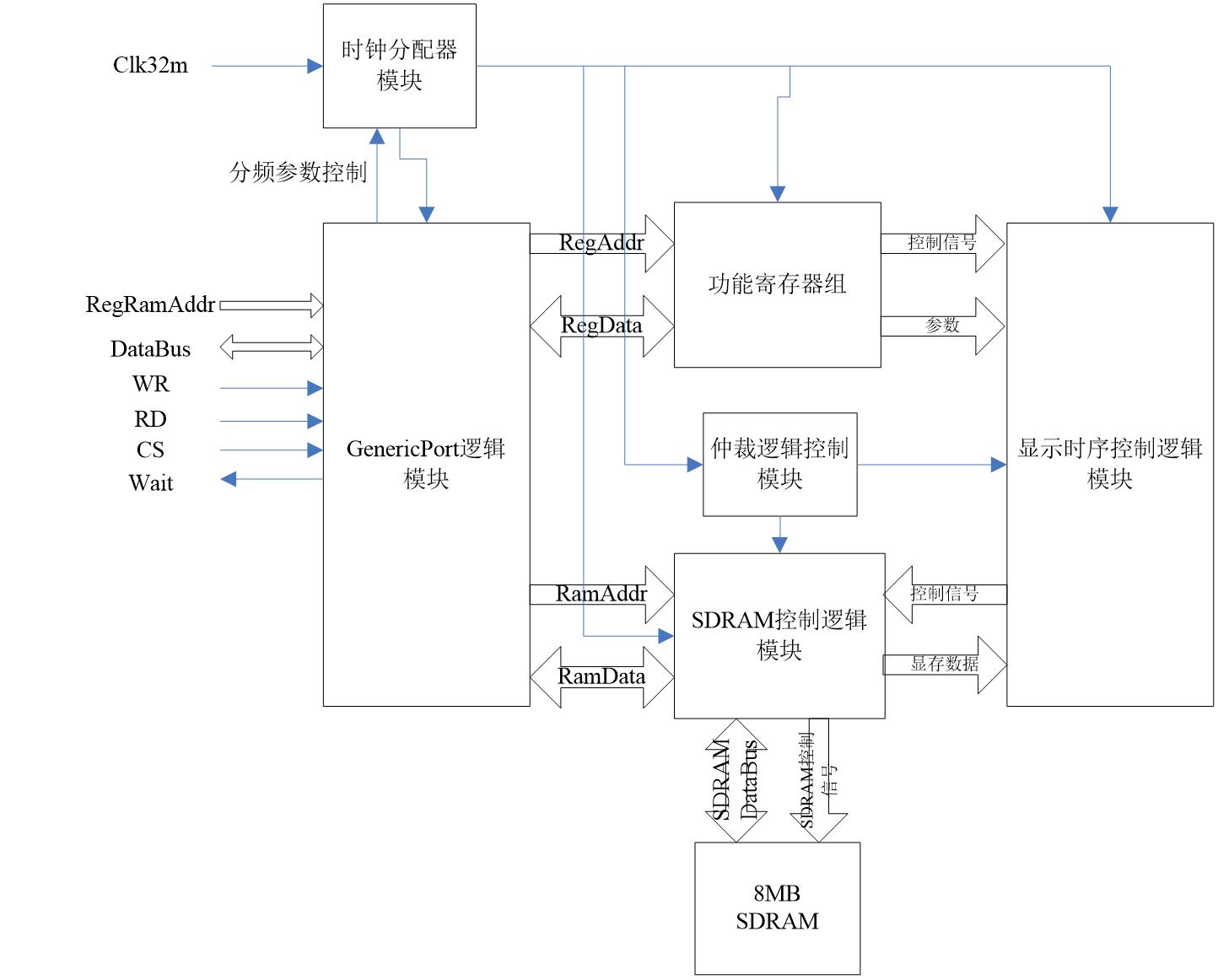

該方案通過 STM32 與 A3P125 FPGA 協同工作,構建適用于醫療監護儀的 LCD/VGA 顯示系統,核心優勢在于:

STM32 主控:負責參數配置、圖形數據傳輸,采用并行總線與 FPGA 高速通信;

A3P125 FPGA:生成顯示時序(像素時鐘、行同步、場同步),驅動 LCD/VGA 屏幕實時渲染波形與數據;

應用場景:多參數監護儀的波形顯示、菜單界面、趨勢圖繪制,當前支持 640×480@60Hz VGA 分辨率。

屏顯模式(Display Mode)

通信接口:STM32 通過 FSMC 并行總線(8/16 位)與 FPGA 連接,寄存器地址映射如下:

寄存器地址功能描述示例值(640×480)0x00分辨率配置0x02(640×480)0x04刷新率配置0x3C(60Hz)0x08圖像緩沖區起始地址0x0000(SDRAM 偏移量)

BMP 數據寫入:STM32 將預處理的 BMP 圖像數據(如心電波形)按行寫入 SDRAM,每像素占用 2 字節(RGB565 格式)。

邏輯框圖

時序參數(640×480@60Hz):像素時鐘:25.175MHz行時序:總周期 800 像素(640 有效 + 160 消隱)場時序:總周期 525 行(480 有效 + 45 消隱)

SDRAM 控制:FPGA 通過地址計數器按行讀取數據,支持突發長度(Burst Length)為 4 的猝發傳輸,提升數據吞吐量。

三、程序示例與代碼框架1. STM32 并行總線配置(FSMC 接口)

/* STM32 FSMC配置 - 16位并行總線 */void FSMC_LCD_Init(void) {

FSMC_NORSRAM_TimingTypeDef Timing = {0};

/* 配置FSMC地址/數據復用模式 */

Timing.AddressSetupTime = 0x0F; // 地址建立時間(15個HCLK周期)

Timing.AddressHoldTime = 0x0F; // 地址保持時間(15個HCLK周期)

Timing.DataSetupTime = 0x3F; // 數據建立時間(63個HCLK周期)

Timing.BusTurnAroundDuration = 0x00; // 總線切換周期(0)

Timing.CLKDivision = 0x00; // 時鐘分頻(0)

Timing.DataLatency = 0x00; // 數據延遲(0)

Timing.AccessMode = FSMC_ACCESS_MODE_A; // 訪問模式A

/* 使能FSMC時鐘與GPIO */

__HAL_RCC_FSMC_CLK_ENABLE();

__HAL_RCC_GPIOB_CLK_ENABLE();

__HAL_RCC_GPIOD_CLK_ENABLE();

__HAL_RCC_GPIOE_CLK_ENABLE();

/* 配置FPGA寄存器寫函數 */

#define FPGA_REG_ADDR ((uint32_t)0x60000000) // FPGA寄存器基地址

#define FPGA_SDRAM_ADDR ((uint32_t)0x64000000) // SDRAM基地址

/* 示例:寫入分辨率寄存器 */

void FPGA_WriteReg(uint8_t reg, uint32_t value) {

*(uint32_t*)(FPGA_REG_ADDR + reg) = value;

}

/* 示例:寫入BMP數據到SDRAM */

void FPGA_WriteSDRAM(uint32_t addr, uint16_t* data, uint32_t len) { uint32_t* sdram_ptr = (uint32_t*)(FPGA_SDRAM_ADDR + addr); for (uint32_t i = 0; i < len; i++) {

*sdram_ptr++ = (uint32_t)data[i];

}

}

}

2. A3P125 FPGA 核心代碼框架(Verilog)

module vga_controller (

input wire clk_25m, // 25MHz像素時鐘

input wire rst_n, // 復位信號

input wire display_en, // 顯示使能

input wire [31:0] reg_addr, // 寄存器地址

input wire [31:0] reg_data, // 寄存器數據

input wire reg_we, // 寄存器寫使能

// SDRAM接口

output wire [12:0] sdram_addr,

output wire [15:0] sdram_dq,

output wire sdram_cke,

output wire sdram_cs_n,

output wire sdram_ras_n,

output wire sdram_cas_n,

output wire sdram_we_n,

output wire sdram_ldqm,

output wire sdram_udqm,

// VGA接口

output wire vga_hsync, // 行同步

output wire vga_vsync, // 場同步

output wire [15:0] vga_rgb // RGB565色彩);

// 寄存器配置模塊

reg [31:0] config_reg[0:15]; // 16個配置寄存器

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

// 初始化寄存器

config_reg[0] <= 32'h00000200; // 分辨率640×480

config_reg[1] <= 32'h0000003C; // 刷新率60Hz

end else if (reg_we) begin

config_reg[reg_addr[4:0]] <= reg_data;

end

end

// 顯示時序生成模塊

reg [11:0] h_counter = 0; // 行計數器(0~799)

reg [11:0] v_counter = 0; // 場計數器(0~524)

wire h_valid = (h_counter >= 0 && h_counter < 640);

wire v_valid = (v_counter >= 0 && v_counter < 480);

wire pixel_valid = h_valid && v_valid;

// 行同步生成

assign vga_hsync = (h_counter >= 656 && h_counter < 752) ? 1'b0 : 1'b1;

// 場同步生成

assign vga_vsync = (v_counter >= 490 && v_counter < 492) ? 1'b0 : 1'b1;

// SDRAM地址計數器

reg [19:0] sdram_addr_counter = 0;

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

sdram_addr_counter <= 0;

end else if (display_en && pixel_valid) begin

sdram_addr_counter <= sdram_addr_counter + 1;

end

end

// SDRAM數據讀取(簡化模型)

assign sdram_addr = sdram_addr_counter[15:3]; // 地址映射

assign sdram_dq = 16'hZZZZ; // 讀操作時浮空,實際需控制SDRAM時序

// SDRAM控制信號(簡化,實際需完整時序)

assign sdram_cke = 1'b1;

assign sdram_cs_n = ~display_en;

assign sdram_ras_n = 1'b1;

assign sdram_cas_n = display_en && pixel_valid ? 1'b0 : 1'b1;

assign sdram_we_n = 1'b1;

assign sdram_ldqm = 1'b0;

assign sdram_udqm = 1'b0;

// VGA色彩輸出(從SDRAM讀取數據)

reg [15:0] current_pixel;

always @(posedge clk_25m or negedge rst_n) begin

if (!rst_n) begin

current_pixel <= 16'h0000;

end else if (display_en && pixel_valid) begin

// 實際項目中需通過SDRAM控制器讀取數據

current_pixel <= 16'h0000; // 示例值,實際為SDRAM數據

end

end

assign vga_rgb = current_pixel;endmodule

四、開發進展與優化方向

當前成果:完成 640×480 分辨率的 VGA 時序生成;實現 STM32 與 FPGA 的并行總線通信(數據傳輸速率≥10MB/s);

待改進點:分辨率擴展:支持 1024×768 等更高分辨率,需升級 FPGA 至更大容量型號;顯示流暢性:優化 SDRAM 突發傳輸效率,降低畫面撕裂;抗干擾設計:增加 EMI 濾波電路,滿足醫療設備電磁兼容性(EMC)要求。

該方案通過 STM32 與 FPGA 的優勢互補,在醫療監護儀顯示領域實現了高性能與低成本的平衡,尤其適合對實時波形顯示有較高要求的場景,如心電圖、血氧波形的動態渲染。

評論