典型的信號完整性問題

典型的信號完整性問題:反射、串擾、電源/ 地噪聲、時序等。

反射

由于傳輸系統阻抗不匹配,會使傳輸的信號不 能被完全吸收,造成部分能量返回。反射造成信號出現過沖(Overshoot)、振鈴(Ringing)、邊沿遲 緩(階梯電壓波)。過沖是振鈴的欠阻尼狀態,邊沿遲緩是振鈴的過阻尼狀態。下圖為信號反射的三種表現形式。

過沖一方面會造成強烈的電磁干擾,另一方面 會損傷后面電路的輸入級,甚至失效。而振鈴會帶 來信號長時間不能穩定,邊沿遲緩帶來信號上升時 間過長,二者都可能帶來信號的時序問題,如時鐘數據同步、建立與保持時間不滿足等。

串擾 Crosstalk

由于導線之間間距過小,當有快速變化的電流 流過導線時會產生交變的磁場,而使鄰近的導線上 感應出信號電壓,稱為串擾(Crosstalk)。 下圖為信號串擾試驗模型,以及受影響信號線上的串擾信號。

串擾一方面是EMC主要根源之一,另一方面, 串擾干擾正常的信號流,有可能造成數據錯誤,是造成誤碼的主要原因之一。問題發生沒有一定規律, 時隱時現,診斷與定位往往花費大量時間與精力。

某單板經常發現工作一段時間后,網口工作異 常,數據傳輸經常有誤碼。詢問供應商,該現象一 般和某芯片的信號受到干擾有關。 檢查 PCB 發現,在相鄰層該信號和一條 100M 信號相重疊,中間沒有地平面分隔,由此引入干擾。

電源/地噪聲

當信號狀態快速改變時,在電源和地上會產生 紋波電流。由于電源和地上的電感的存在,信號突 變產生的尖峰電流將使電源和地上出現電壓的波 動。系統幾十甚至上百個信號同時發生狀態改變時, 有可能造成系統的誤動作。由于電源/地噪聲的復雜 性,有時單獨作為電源完整性(Power Integrity)來 研究。

歷史參考文檔:

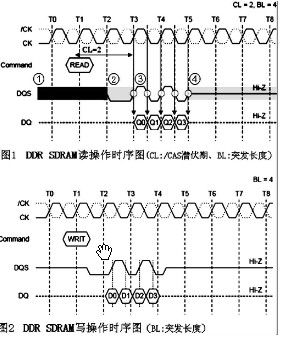

時序問題

系統中數據的提取通常是由時鐘信號的上升沿 或下降沿觸發,按照一定的節拍進行,數據應該及 時到達接收端并進入穩態。數據的超時延時和數據 的信號畸變都會造成數據的讀取錯誤。接收端信號 由于出現嚴重的振鈴現象,部分進入非穩定狀態, 會使數據不能被可靠地提取,造成誤碼問題。

歷史參考文檔:

信號完整性設計方法

嚴格控制關鍵信號的 PCB 走線長度

信號完整性問題主要是 PCB 走線過長造成的。 如果在設計前期,我們能夠找出關鍵信號,并對走線長度進行控制,就可以有效地抑制信號反射,保證信號質量。所以我們需要研究器件的數據手冊, 確定信號最快上升與下降時間,估算臨界走線長度, 對于時鐘、高速數據流信號尤其要注意長度控制。

合理規劃走線的拓撲結構

走線的拓撲結構是指一根走線的布線順序及布 線結構,如菊花鏈和星形分布等。同時,需要采用 合適的匹配方式,如源端匹配、終端匹配等。我們 需要了解電路的設計原理,驅動順序與信號本身特 點,采用合適的拓撲與匹配方式。

有效控制 PCB 特征阻抗

在多層線路板中,信號完整性性能良好的關鍵 是使它的特性阻抗在整條線路中保持恒定。目標是 使所有線路的特性阻抗滿足一個規定值,通常在 25 歐姆和 70 歐姆之間。所以在設計時,就需要對 PCB 走線特征阻抗進行計算,確定合理的走線寬度與其 它設計參數;在 PCB 加工時,表明阻抗要求;PCB 加工后,需要采用儀器對特征阻抗進行驗證。

設計仿真技術

在 PCB 設計過程中,采用軟件進行仿真。在系 統設計時,對模塊布置進行仿真;在單板布局時, 可以進行前仿真,確定器件布局;在走線時,進行 后仿真,保證走線質量。通過仿真,事先可以預測 到信號的設計質量,及時調整設計策略,預先預防, 而不是事后補救。

其它可采用技術

在設計時,需要從電路設計、布局、布線、電源系統等方面進行考慮。如在電路設計時,合理選 擇驅動器件,盡量采用同步設計,避免異步設計, 高速信號采用差分信號,為集成電路芯片添加去耦 電容;布局時,注意數字與模擬信號分開,合理設 計單板的疊層,器件按照速度合理布局;布線時,注意少打過孔,布線遵循 3W 原則;電源設計時, 注意低阻抗連接,層疊遵循 20H 原則等。

評論