基于 HalideIR 的敏捷硬件等價性驗證框架

——從形式化方法到自動化工程實踐

一、敏捷硬件的崛起:從“慢工出細活”到“快速創新”

在傳統的芯片開發中,一個從算法原型到可綜合 RTL 的設計流程往往需要經歷數月甚至數年的反復迭代。

這一漫長的周期嚴重制約了硬件領域的創新速度,與軟件領域的“快速迭代”形成鮮明對比。

隨著 AI 芯片、可重構計算與異構加速器的興起,設計者迫切希望像開發軟件那樣,能夠在高抽象層快速修改算法、調整結構、重新生成硬件。

**敏捷硬件設計(Agile Hardware Design)**應運而生:它借鑒軟件工程的敏捷理念,使硬件開發具備更高的靈活性和可重構性。

然而,頻繁迭代帶來的新問題也隨之出現——每一次調度策略、并行結構或流水線深度的修改,都可能改變設計的行為。

為了確保新的版本仍與原始規格保持一致,**自動化等價性驗證(Equivalence Checking)**成為敏捷設計流程中不可或缺的環節。

二、HalideIR:敏捷硬件的核心橋梁

在這一背景下,HalideIR 扮演了連接高層算法與底層實現的關鍵角色。

HalideIR 起源于圖像處理與深度學習編譯系統,其設計思想是**“算法邏輯”與“執行調度”相分離**:

算法部分描述計算意圖;

調度部分定義如何執行,包括循環展開、并行化、向量化等。

這種抽象機制使得開發者可以在不修改算法的前提下,快速嘗試不同的優化策略。

更重要的是,HalideIR 可以被映射到多種目標語言(如 C/C++、SystemC、RTL),從而成為通用的中間表示層(Intermediate Representation, IR)。

近年來,多個敏捷硬件框架,如 HeteroCL、HeteroHalide、Halide-HLS 等,均以 HalideIR 為核心中間層。這意味著——

若能在 HalideIR 層面實現自動等價驗證,將能直接服務于整個敏捷硬件生態。

三、等價性驗證的基本思路與難點

等價性驗證的目標是:

給定兩個設計版本,在相同輸入條件下,判斷它們是否生成完全相同的輸出。

在 HalideIR 層面,這一問題可轉化為兩份 HalideIR 抽象語法樹(AST)的結構與行為比較。

然而,直接在全設計級別進行符號執行(Symbolic Execution)往往遭遇**路徑爆炸(Path Explosion)**問題,尤其是在深度學習類加速器中,大量循環與并行結構導致求解復雜度急劇上升。

此外,每次設計修改后手動構造驗證“測試封裝”(test harness)也十分耗時。

因此,要讓驗證過程真正匹配“敏捷開發”的節奏,必須解決可擴展性與自動化兩大問題。

四、提出的解決方案:可擴展的等價性驗證框架

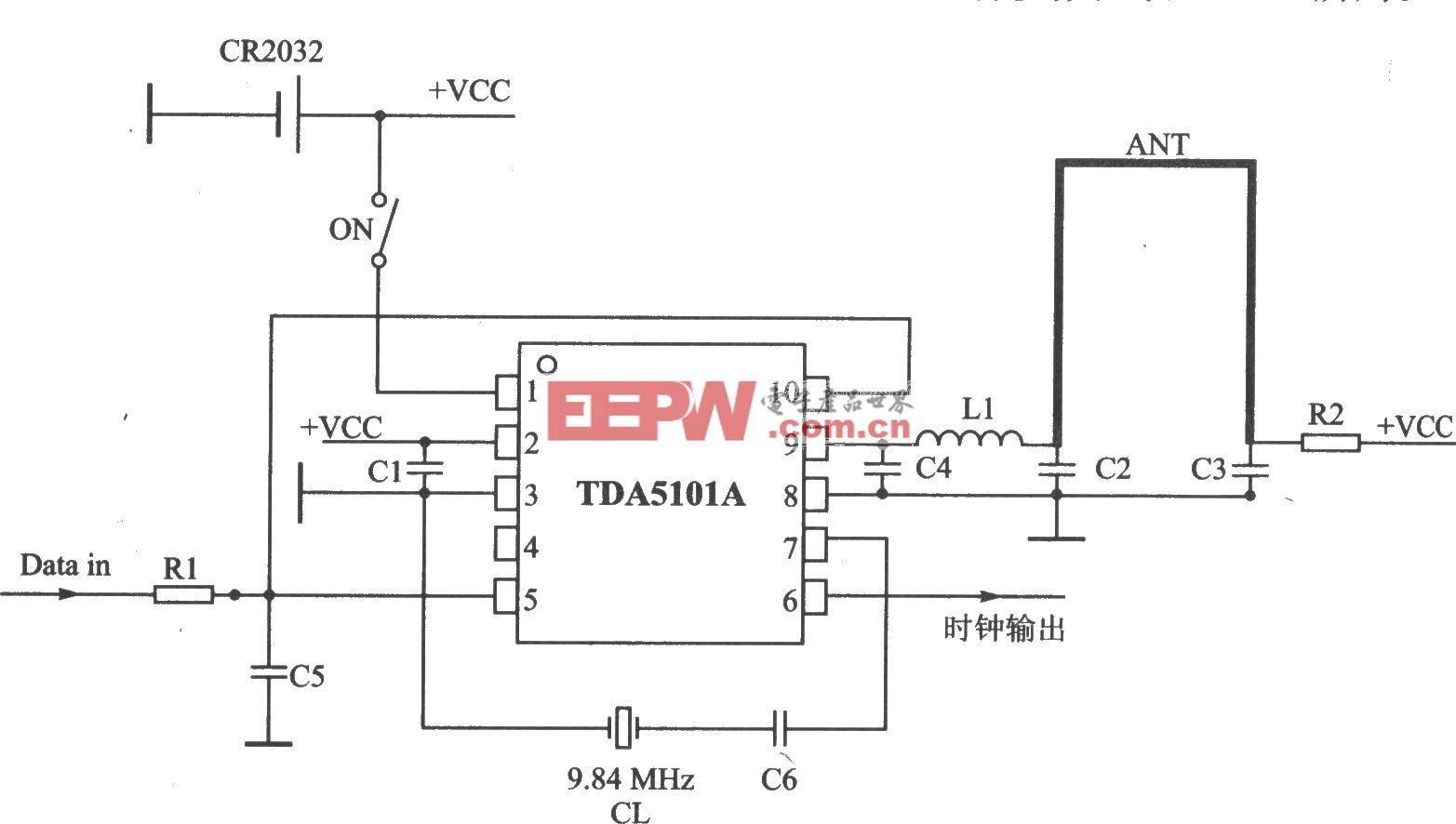

針對上述痛點,研究團隊設計了一套基于 HalideIR 的自動等價驗證框架,其總體思路如圖示(原文 Figure 2)所示。

核心流程包括以下五個階段:

HalideIR 提取:從敏捷硬件 DSL(如 HeteroCL)中編譯出兩個版本的 HalideIR;

結構分析(IR Checker):比較兩份 AST 的結構,找出差異節點;

最小檢查單元劃分(Minimal Check Unit):將驗證任務分解為多個獨立的小模塊;

測試封裝自動生成(Test Harness Generator):自動識別輸入/輸出變量并生成驗證代碼;

符號執行驗證(Symbolic Engine):基于 KLEE 工具,對各最小單元進行自動等價檢測。

通過這種自頂向下的分解式驗證策略,框架將原本龐大復雜的驗證任務化整為零,實現了在可接受時間與內存范圍內的高效求解。

五、關鍵技術詳解

1. 基于 HalideIR 結構的最小檢查單元劃分

HalideIR 中的“Stage”天然對應一組計算操作,是算法的最小語義塊。

框架通過遍歷兩份 HalideIR 的 AST,比較節點類型與操作數,自動標記結構不一致的 Stage。

每個被標記的 Stage 即作為一個“最小檢查單元(MCU)”,單獨進入符號執行驗證。

這一思路不僅提升了可擴展性,也為后續調試提供了定位依據——當驗證失敗時,設計者可直接定位到具體 Stage 的不一致操作。

2. 自動生成測試封裝代碼

每個最小檢查單元本身并非完整模塊,需要額外的輸入輸出封裝以供符號執行。

框架通過分析 HalideIR 中的 Allocate 與 Store 節點,自動判斷:

輸入變量:未在本單元中分配或寫入;

輸出變量:由本單元寫入但未在內部定義。

通過這一依賴分析,系統可自動生成可執行的 C++ 驗證代碼,確保符號執行引擎能夠獨立運行該單元。

這一步極大減少了人工測試腳本的編寫工作量。

3. Uninterpreted Function 優化機制

在大型設計中,不同 Stage 之間存在層級關系。若某子模塊已被驗證為等價,則可將其替換為“未解釋函數”,在后續驗證中跳過展開。

這種“遞歸抽象”優化顯著減少了求解路徑數量,從而緩解路徑爆炸問題。

驗證引擎在遇到已認證模塊時自動進行替換,使整個流程呈現出漸進式收斂特性。

六、框架應用與實驗結果

研究團隊在開源深度學習加速器 VTA(Versatile Tensor Accelerator) 上進行了驗證實驗。

他們分別比較了以下三種實現:

hVTA:原始參考設計;

sVTA:順序執行版本;

uVTA:引入微操作并行的版本。

實驗環境使用 12 核 AMD Ryzen 5900X 處理器與 128GB 內存。

若直接對整個設計進行驗證,KLEE 工具無法在 24 小時內完成符號執行;

而在啟用分階段驗證與 uninterpreted function 優化后,驗證時間顯著下降:

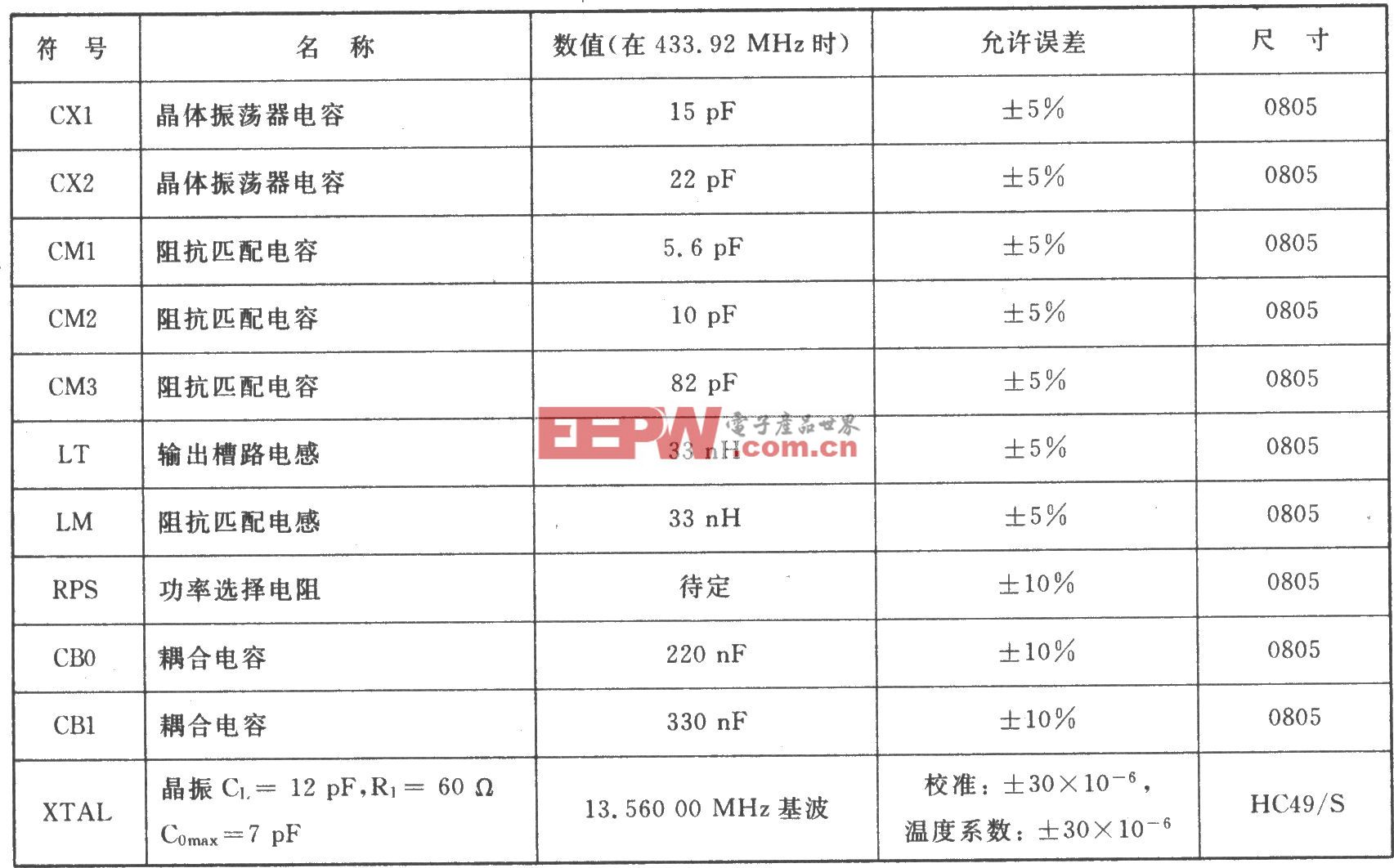

| 驗證組合 | 優化前 | 優化后 | 內存占用 | 檢測結果 |

|---|---|---|---|---|

| sVTA vs hVTA | 超時(>24h) | 65秒 | 128MB | 檢出2處功能不一致 |

| uVTA vs hVTA | 超時(>24h) | 1238秒 | 2.3GB | 檢出3處功能不一致 |

值得注意的是,所有檢測出的不一致均是手寫單元測試未能發現的潛在問題。

這驗證了形式化方法在敏捷硬件驗證中的工程價值。

七、發現的典型問題與分析

在實驗中,框架捕獲了三類具有代表性的設計問題:

指令格式偏移問題:

sVTA 中將 ALU 操作碼從 2 位擴展至 3 位,導致指令字段錯位,執行結果與參考實現不符。未初始化存儲錯誤:

uVTA 中新增了 pad_value 控制位,但初始化時未置零,導致 SRAM 填充值錯誤。API 誤用問題:

設計者在 HeteroCL 中使用 Python 賦值語句替代hcl.update(),導致部分內存未被清零。

該問題無編譯警告,極易在人工測試中被忽略。

這些案例充分說明,在敏捷硬件中,形式化驗證不僅能發現邏輯錯誤,還能揭示框架級 API 使用不當的問題。

八、框架意義與未來展望

通過本研究提出的框架,敏捷硬件設計終于具備了一種與軟件持續集成相對應的自動化驗證機制。

它為 HalideIR 生態下的硬件設計提供了:

高度自動化的驗證流程;

可擴展至復雜設計的分層策略;

精確到 Stage 級的錯誤定位能力。

展望未來,若將該框架進一步擴展至 TVM、TensorIR 等高層編譯系統,并結合并行 SMT 求解與機器學習驅動的結構相似性分析,將能在性能與智能化程度上更進一步,為“軟硬件協同敏捷設計”奠定驗證基礎。

【編輯點評】

本研究以工程化視角重新定義了硬件等價性驗證的邊界。

它不僅是形式化驗證技術的延伸,更是敏捷硬件實踐中“自動正確性保證”的關鍵一環。

在硬件設計向 DSL 與高層綜合過渡的今天,這種基于 HalideIR 的驗證框架,標志著驗證工具鏈正在從“事后檢測”邁向“過程保障”。

未來,隨著更多 AI 芯片與異構計算平臺采用這一理念,自動化等價驗證將成為敏捷硬件設計的“標配模塊”。

評論