硅生命周期管理對芯片架構(gòu)的現(xiàn)實影響

通過 SLM 設計具備韌性的芯片,有助于對抗老化效應、安全威脅,并以更高良率更快進入市場。

硅生命周期管理(SLM)正在改變芯片架構(gòu)。通過利用從制造階段到在現(xiàn)場服役直至生命周期結(jié)束所獲得的數(shù)據(jù),SLM 賦能設計人員構(gòu)建更智能、更具韌性且更安全的半導體器件。

這些數(shù)據(jù)可用于改進未來設計、縮小設計裕量,并在芯片整個生命周期內(nèi)持續(xù)優(yōu)化性能和功耗效率。此外,對完整生命周期的理解還能使芯片設計更能抵御老化效應和新型安全威脅,并具備在部署后監(jiān)測并潛在緩解問題的能力。

“SLM 的終極承諾在于發(fā)現(xiàn)那些原本幾乎不可能被發(fā)現(xiàn)的問題,從而縮短生命周期,并提升良率、可靠性、安全性、上市時間以及運營成本,”Simon Rance 表示,他是 Keysight EDA 工藝與數(shù)據(jù)管理業(yè)務的總經(jīng)理兼業(yè)務單元負責人。“將 SLM 組件和模塊嵌入設計中,以支持遙測以及測試和調(diào)試能力,本身就是一項挑戰(zhàn),而且往往需要具備相當專業(yè)知識的專家才能高效完成。盡管前期投入相當大,但在后端會獲得豐厚回報,因為你采用的是一種左移式方法,幾乎可以實時發(fā)現(xiàn)問題,從而更早、更快速地進行迭代和優(yōu)化。”

通過在芯片和封裝中插入監(jiān)控器所收集的數(shù)據(jù),還可以改進失效分析和質(zhì)量控制,加速良率爬坡,并幫助更快地識別問題的根本原因。反過來,這可以縮短上市時間,同時為依賴長期性能和可靠性的全新服務和商業(yè)模式打開大門,例如汽車或消費電子行業(yè)。

“這要求我們從芯片內(nèi)部去看問題,并在不同物理參數(shù)上具備極高分辨率的可視性,從而支撐我們按芯片級別來刻畫其預期測量表現(xiàn)的能力,”Noam Brousard 表示,他是 proteanTecs 的解決方案工程副總裁。“我們在芯片內(nèi)部部署了高分辨率監(jiān)控器,能夠消除噪聲因素,直接觀察工藝本身。我們還做了一些更新穎的事情,比如觀察路徑延遲,主要是在測試的后期階段進行測量,并將其與我們在前硅階段通過仿真得到的預期結(jié)果進行比較。我們在比較數(shù)百萬條路徑的時序裕量,或者數(shù)百萬條路徑的延遲,與仿真結(jié)果進行對照。”

盡管 SLM 的優(yōu)勢顯而易見,但將這些能力集成到芯片設計中也引入了新的復雜性和必須在整個開發(fā)過程中加以解決的考量。這引出了一個重要問題:SLM 策略應如何根據(jù)特定用例進行定制,以及由此帶來的架構(gòu)決策。

“硅生命周期管理的一個挑戰(zhàn)在于它是依賴用例的,”Randy Fish 表示,他是 Synopsys 的 SLM 產(chǎn)品線總監(jiān)。“今天的測試非常復雜,但你想要實現(xiàn)的目標基本上還是清楚的。而 SLM 作為測試的近親,則更加以用例為驅(qū)動。存在在現(xiàn)場的用例,在這些場景中你會在任務模式下使用這些信息;也存在在測試階段的用例,你會在掃描測試或系統(tǒng)級測試期間使用這些信息。根據(jù)你試圖實現(xiàn)的目標不同,對架構(gòu)的影響也會不同。如今在一顆高度復雜的芯片上,比如一個大型芯片用于 AI 推理或訓練,你可能會有數(shù)百個感測點的 PVT(工藝、電壓、溫度)監(jiān)控器。這已經(jīng)不再只是芯片角落里的一個熱二極管,而是一個復雜的基礎設施,數(shù)據(jù)匯入一個 PVT 控制器——這是一個 RTL 控制器,多個監(jiān)控器都可以接入其中。你還可以有多個控制器,它們通過 APB 或其他接口,最終通常會連接到系統(tǒng)控制處理器(SCP)。很多人使用 Arm 控制器或其他來源。然后數(shù)據(jù)可以在那里集中。或者在像 ABS 這樣的場景中,你可能不僅希望這些數(shù)據(jù)被送入一個軟件解決方案中,例如用于在芯片外部管理 PMIC,還希望進入一個硬件解決方案中,以便能夠非常快速地做出響應。因此你會在芯片內(nèi)有 LBO 等具備極快響應能力的模塊,希望它們在幾個周期內(nèi)完成響應,而不是像 PMIC 那樣以慢得多的頻率響應。這些可以由軟件管理,因此架構(gòu)會根據(jù)你試圖解決的問題集而呈現(xiàn)出極大的多樣性。”

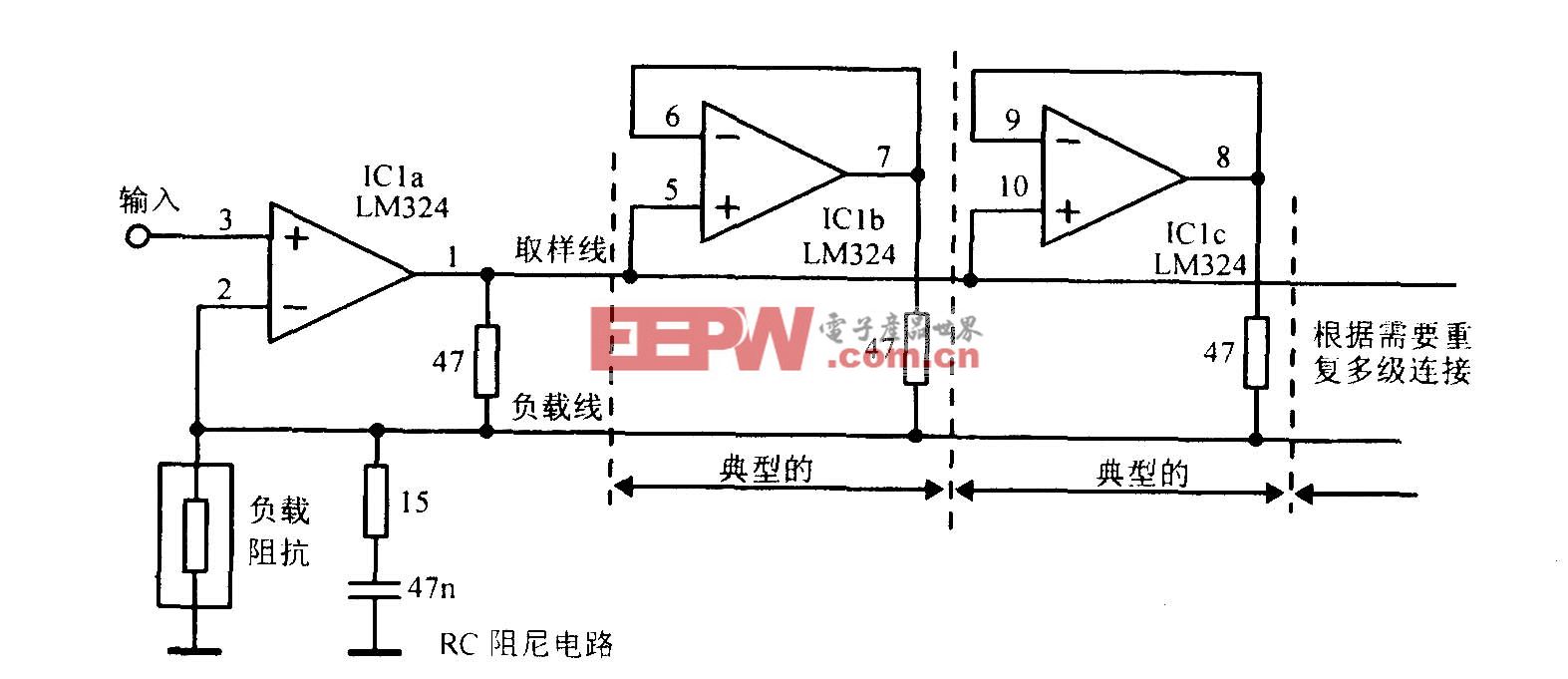

圖 1:SLM 加測試解決方案棧的示例架構(gòu)。來源:Synopsys

隨著芯片架構(gòu)師權(quán)衡這些因素并應對 SLM 集成的復雜性,實際的實現(xiàn)細節(jié)變得至關(guān)重要。正是在這里,專家見解和真實案例為塑造有效生命周期管理策略的挑戰(zhàn)和解決方案提供了啟示。

“首要考慮因素是清楚地了解需要哪些類型的傳感器/監(jiān)控器,需要多少個,以及它們應放置在哪里,”Geir Eide 表示,他是 Siemens EDA Tessent 硅生命周期解決方案的產(chǎn)品管理高級總監(jiān)。“一方面,可以重新利用可測性設計(DFT)結(jié)構(gòu)來支持高質(zhì)量的在現(xiàn)場測試。由于這些結(jié)構(gòu)在設計中已經(jīng)存在,對設計及設計流程的影響相對較小。另一方面,一些傳感器(例如裕量監(jiān)控器)對物理放置非常敏感,整體結(jié)果質(zhì)量也取決于在設計中插入了多少傳感器。而傳感器的放置本身也具有挑戰(zhàn)性,因為最敏感的路徑直到布局布線之后才能確定,而在那個階段你通常并不希望再向設計中插入額外的對象(傳感器)。”

Eide 還指出,另一個重要考量涉及從所有傳感器收集數(shù)據(jù)所使用的基礎設施。“測量將以多高的頻率進行?是在功能運行期間持續(xù)測量,還是作為診斷測試的一部分偶爾測量?需要收集多少數(shù)據(jù)?重用功能總線或其他現(xiàn)有基礎設施(例如 IEEE 1687 IJTAG)可能是有利的,但這未必可行,這取決于帶寬需求以及傳感器運行時機的要求(例如是在完全功能模式下還是在結(jié)構(gòu)測試期間)。尤其對于復雜設計,數(shù)據(jù)量大、監(jiān)控器多,采用一種可良好擴展的方法非常重要。”

所有這些都意味著,SLM 正在改變復雜 SoC 的架構(gòu)方式。“隨著工藝縮放極限收緊、可靠性裕量壓縮,設計團隊正在硅中嵌入密集的傳感器、監(jiān)控器、計數(shù)器和跟蹤點網(wǎng)絡,以暴露有關(guān)電壓跌落、熱梯度、時序裕量、老化以及工作負載行為的實時信息,”Andy Nightingale 指出,他是 Arteris 的產(chǎn)品管理與市場副總裁。“這些數(shù)據(jù)不再只是后硅階段的輔助手段——它正成為一種架構(gòu)輸入,從首次上電到生命周期結(jié)束,塑造功耗、性能、可靠性和安全性的管理方式。”

對于芯片架構(gòu)師而言,SLM 的存在要求一種思維轉(zhuǎn)變。“監(jiān)控基礎設施必須在架構(gòu)階段盡早規(guī)劃,而不是在 RTL 階段才事后補加。這包括定義傳感器的位置、其數(shù)據(jù)如何匯聚,以及遙測流量如何與對性能至關(guān)重要的流量共存。互連結(jié)構(gòu)在這里扮演著核心角色:現(xiàn)代 NoC 必須提供隔離性、可預測的時延以及韌性特性,使 SLM 流量能夠在大規(guī)模條件下安全傳輸,”Nightingale 說。

隨后,在技術(shù)基礎確立之后,芯片架構(gòu)師還必須關(guān)注在多樣化系統(tǒng)環(huán)境中實現(xiàn) SLM 的現(xiàn)實問題,在先進 SLM 監(jiān)控的復雜需求與復雜 SoC 架構(gòu)固有的運行挑戰(zhàn)之間取得平衡。

“SLM 系統(tǒng)可以與整體 SoC 架構(gòu)緊密耦合,也可以松散耦合,這取決于已定義的需求,”Vikram Karvat 表示,他是 Movellus 的首席運營官。“可以從兩個方面來看待 SLM——傳感器和執(zhí)行器。傳感器可以松散耦合,對架構(gòu)影響較小。例如,一個提供時序裕量或工藝信息的傳感器網(wǎng)絡,可能只需通過 APB 等標準接口與這些傳感器交互即可。當你不僅僅是在感知,而是要基于傳感器輸出采取實時動作時,執(zhí)行器就會發(fā)揮作用。此時,感知與執(zhí)行相結(jié)合的功能實現(xiàn)就需要提前規(guī)劃,因為 SoC 架構(gòu)師正是利用這種組合在特定情形下實現(xiàn)性能目標和架構(gòu)保證。規(guī)劃可能涉及時鐘和電源域的劃分、DVFS/DFS 架構(gòu)及其能力、布局考慮、封裝設計、PDN 設計等。隨著時間推移,豐富的遙測數(shù)據(jù)當然還會形成一個前饋環(huán)路,用于下一代硅設計和架構(gòu)決策。這可以從兩個維度來理解——感知與執(zhí)行,以及當前硅與后續(xù)硅世代。”

除了硬件方面的考量,SLM 還應包括能夠掛接到設計中的軟件,并需要在實時和在役狀態(tài)下進行驗證。“鑒于我們公司在測試與測量領(lǐng)域的根基,我們正在尋找新的方法,盡可能早地在設計周期中引入所有這些能力,”Keysight 的 Rance 表示。“這確實具有挑戰(zhàn)性,但我們發(fā)現(xiàn),當你把事情做對,并運用我們所具備的能力和專業(yè)知識時,通常可以更快地啟動,并幫助客戶更快地實現(xiàn)目標。這幾乎像是在整個生命周期中牽著手前行,而不是只面對一個團隊。設計團隊、測試團隊、測量團隊、驗證團隊和制造團隊在傳統(tǒng)上并不常交流,通常只是一個團隊向下一個團隊交接。挑戰(zhàn)在于如何讓他們協(xié)同合作,如何讓他們在合適的時間共享正確的信息,以及這些流程如何實現(xiàn)自動化。這正是工作流發(fā)揮作用的地方——它們幫助把所有團隊、所有要素和所有數(shù)據(jù)拉通。如何擁有一個能夠支撐并追溯這一切的單一真實數(shù)據(jù)源?”

Siemens 的 Eide 提到了兩個 SLM 實施示例。“已有許多超大規(guī)模云服務公司報告了在兆規(guī)模數(shù)據(jù)中心中現(xiàn)場錯誤的影響,”他說。“這些錯誤往往非常難以檢測。其中許多可以追溯到與時序相關(guān)的問題,因為晶體管的性能會隨時間變化。亞馬遜云服務曾發(fā)表論文,介紹如何擴展通常用于制造測試的可測性設計方法和基礎設施,通過‘在現(xiàn)場 IC 監(jiān)控、更換失效部件,以及定位現(xiàn)場診斷失敗’來解決此類與時序相關(guān)的問題。”

在第二個示例中,Meta 描述了其 IC 調(diào)試架構(gòu)如何支持在現(xiàn)場的軟件調(diào)試與分析,這是監(jiān)控之后的步驟。在這里,重點在于軟件性能,而非 IC 缺陷或老化。

SLM 還可用于功耗監(jiān)控與優(yōu)化。Movellus 的 Karvat 提到了電壓跌落緩解、電源網(wǎng)絡可視化以優(yōu)化 DVFS 設定點、主動 DFS 以及 DVFS 控制。目標是實現(xiàn)代碼重分區(qū)或調(diào)度,以平滑電流消耗或避免熱點,并通過智能自適應來緩解老化效應。

其他公開示例表明,這已經(jīng)在影響設計選擇。“Arteris 的 FlexNoC 和 Ncore IP 已被 AMD、Mobileye 和 Blaize 等合作伙伴用于 AI、汽車以及基于 chiplet 的設計中,在這些設計里,互連不僅用于數(shù)據(jù)傳輸,還用于在大型分布式系統(tǒng)中路由 RAS、調(diào)試和監(jiān)控信息,”Nightingale 指出。

這些實際案例和技術(shù)細節(jié)突顯了 SLM 解決方案如何從理論概念演進為現(xiàn)代芯片設計中的關(guān)鍵組成部分。隨著行業(yè)采用更加復雜的傳感器網(wǎng)絡、集成化工作流和自適應架構(gòu),SLM 的重要性只會不斷提升,為硅開發(fā)和生命周期管理的新范式奠定基礎。

“在以 AI 驅(qū)動、自我演進的設計自動化為基礎的背景下,SLM 不僅僅是一種架構(gòu)增強,”William Wang 表示,他是 ChipAgents 的 CEO。“它成為下一代代理式 EDA 系統(tǒng)的數(shù)據(jù)與智能基底。在傳統(tǒng)設計流程中,架構(gòu)師基于仿真和前硅假設,在性能、功耗和可靠性之間做出靜態(tài)權(quán)衡。而有了 SLM,真實世界的遙測數(shù)據(jù)會直接反饋到設計生態(tài)中,使 AI 代理能夠持續(xù)從已部署的硅中學習。這將前端流程轉(zhuǎn)變?yōu)橐粋€活的、自適應的閉環(huán),其中 RTL、驗證策略甚至架構(gòu)模板都會根據(jù)現(xiàn)場數(shù)據(jù)動態(tài)演進。”

對于自我演進的設計代理而言,SLM 數(shù)據(jù)既是上下文,也是事實依據(jù)。“工藝偏差、工作負載行為以及退化模式不僅被監(jiān)測,還被用于重新訓練優(yōu)化模型,”Wang 說。“代理可以提出漸進式的架構(gòu)改進建議,重新參數(shù)化模塊,甚至重新綜合局部邏輯塊,以獲得更高的效率和更長的壽命。從這個意義上說,芯片成為其自身設計反饋機制的一部分,彌合了設計意圖與運行現(xiàn)實之間的鴻溝。”

要充分發(fā)揮這一點,前端架構(gòu)需要具備模塊化、可參數(shù)化和自省能力,并以內(nèi)嵌、可被代理讀取的設計意圖構(gòu)建,使 AI 代理能夠自主推理權(quán)衡。“EDA 環(huán)境必須通過標準化 API 和語義層暴露 SLM 數(shù)據(jù),使代理無需人工干預即可理解,”他說。“安全性和數(shù)據(jù)溯源機制在這里同樣至關(guān)重要:代理必須信任其所采取行動所依據(jù)的數(shù)據(jù),確保任何設計演進都是安全、可驗證且可解釋的。”

最終,ChipAgents 的愿景是利用 SLM 將硅同時變成產(chǎn)品和老師。“每一顆部署在現(xiàn)場的芯片都會為集體智能做出貢獻,塑造未來世代的設計。EDA 的前沿正在從靜態(tài)自動化轉(zhuǎn)向主動協(xié)作,在這一連續(xù)反饋生態(tài)中,智能設計代理與具備自我感知能力的芯片共同演進。最好的希望或許在于通過 AI 代理連接前硅與后硅,”Wang 補充道。

鑒于這些創(chuàng)新和戰(zhàn)略考量,SLM 技術(shù)的集成正在為系統(tǒng)架構(gòu)師帶來新的復雜性和機遇。隨著組織從理論和早期部署邁向?qū)嶋H實施,下一步是理解如何在真實設備和工作流中利用 SLM 數(shù)據(jù)和基礎設施以獲得切實收益。

面向 SLM 新手

對于此前未在其器件中引入 SLM 監(jiān)控器的架構(gòu)師而言,需要提出若干問題,而這些問題都指向具體用例。

“首先,我們打算如何使用這些數(shù)據(jù)?”Synopsys 的 Fish 表示。“最容易實現(xiàn)的目標是,‘我只是想訪問這些數(shù)據(jù)。我們從來無法一直看到芯片內(nèi)部發(fā)生了什么,所以我希望具備基礎設施和遙測能力,能夠?qū)崟r查看溫度、裕量、電壓和毛刺的變化。’或者,‘我們希望在一段時間內(nèi)收集數(shù)據(jù),然后再將其導出芯片。’數(shù)據(jù)將在芯片上如何收集?由哪個處理器來收集?存儲在哪里?是緩存在內(nèi)存中,還是通過主板上的基板管理控制器進行服務,或者是在機架頂部進行服務,甚至像汽車那樣一路回傳到云端?這意味著遙測架構(gòu)是架構(gòu)師非常關(guān)心的內(nèi)容。其中一部分歸結(jié)為速率和帶寬。如果你只是偶爾觸發(fā)一次,或者只在超過某個閾值時告警,也許速度要求較低,不需要緩沖太多數(shù)據(jù)。但如果你試圖流式傳出大量信息來分析某個工作負載,那么所使用協(xié)議的速度、緩沖區(qū)大小,以及你多頻繁地對數(shù)據(jù)進行處理以將其壓縮為有用信息,就都非常關(guān)鍵,因為你不可能一直把所有數(shù)據(jù)從芯片中流式輸出。具備智能處理能力非常重要,因為這會影響你系統(tǒng)控制處理器的規(guī)模選擇。是 M0?還是 M3?今天需要多大規(guī)模?它運行 Linux 還是 RTOS,或者是裸機?”

在這里,特定 IP 可能會非常有用,例如通過 PCIe、USB 或其他通信協(xié)議來運行掃描序列,以支持在現(xiàn)場掃描測試,這隨后就成為在現(xiàn)場體驗的一部分,使系統(tǒng)能夠運行系統(tǒng)級測試,或者出于功能安全(FUSA)的目的運行安全測試。對在現(xiàn)場結(jié)構(gòu)測試的需求正在增加,以嘗試隔離失效器件中發(fā)生的問題,例如靜默數(shù)據(jù)損壞場景,而測試是理解這些問題的關(guān)鍵組成部分。

“我們在你不得不通過冗余、增加裕量或加大防護帶來補償之前,就標記出那些離群芯片,”proteanTecs 的 Brousard 表示。“我們不僅能看到某條路徑是否未達到預期的時序裕量,即便達到了,也能判斷它究竟有多接近極限。這是一種看待芯片的全新方式——不僅僅是通過或失敗,而是即使通過了,也可能只是勉強通過,很可能在其生命周期的很早階段就發(fā)生失效。”

在這些基礎性問題和實際考量的指引下,邁向有效 SLM 部署的旅程需要對可用的架構(gòu)選擇和實現(xiàn)策略進行更深入的探索。通過應對數(shù)據(jù)處理、測試基礎設施以及系統(tǒng)集成方面的細微差別,架構(gòu)師可以更好地定位其設計,從而在硅生命周期的各個階段充分實現(xiàn) SLM 所帶來的收益。

“歸根結(jié)底,還是要看 SoC 架構(gòu)試圖解決什么問題,”Karvat 說。“是功耗優(yōu)化、性能優(yōu)化、性能保證、封裝和測試成本優(yōu)化,還是為上層軟件提供信息,等等?這個問題將決定他們需要考慮什么。SLM 可以很簡單,也可以很復雜,其使用方式也可以不斷演進。”

在做出 SLM 選擇時,Karvat 表示,芯片架構(gòu)師和設計人員應考慮從臺架表征、任務模式到在現(xiàn)場測試的各種 SLM 用途,以及如何在多個階段復用同一套基礎設施。“每一顆 SoC 都不同,因此要通過選擇可在后硅階段調(diào)節(jié)、并可在不同設計中復用的組件來保持靈活性。同時,使用開放/標準的硬件和軟件接口,因為沒有任何單一供應商能夠提供你所需的一切。你需要能夠混合搭配組件,并擁有可在異構(gòu)環(huán)境中適配需求的軟件基礎設施。軟件和固件不一定要免費,但必須具備可適應性,以滿足包括定制在內(nèi)的需求。”

架構(gòu)師和設計人員還需要認識到,SLM 覆蓋整個生命周期:設計、bring-up、優(yōu)化、現(xiàn)場可靠性以及車隊級分析,Arteris 的 Nightingale 觀察到。“嵌入傳感器只是開始。NoC 必須支持遙測的 QoS 隔離、敏感監(jiān)控數(shù)據(jù)的安全域,以及為 DVFS 回路、錯誤處理框架和自愈機制提供的控制路徑。驗證也必須擴展到 SLM 覆蓋,包括故障注入、時間戳同步和事件關(guān)聯(lián)。只有當遙測數(shù)據(jù)能夠無縫連接到固件、驅(qū)動和分析框架時,其價值才能真正體現(xiàn)。隨著行業(yè)邁向更大規(guī)模的多芯片 AI 加速器、汽車安全平臺以及超大規(guī)模云級 chiplet,SLM 在架構(gòu)中的占比將持續(xù)擴大——使可觀測性和生命周期智能與計算吞吐量或內(nèi)存帶寬一樣基礎。”

從根本上講,SLM 是一個非常寬泛的概念。“對于任何特定的 SLM 實現(xiàn)而言,重要的是聚焦并理解具體目標是什么,我們試圖解決哪些問題,”Siemens EDA 的 Eide 補充道。“你是想檢測問題,還是具備診斷和解決問題的能力?針對某一需求,可能有多種解決方式,從使用傳感器到基于軟件的解決方案不一而足,而聚焦的范圍有助于提高成功概率。也許對設計人員來說不那么顯著,但總體而言非常重要的一點是,SLM 不僅僅關(guān)乎芯片本身,它關(guān)乎整個系統(tǒng)。在芯片之外,還有許多拼圖要素,例如數(shù)據(jù)傳輸、安全性和分析。如果缺少這些部分,傳感器和監(jiān)控器的價值就大打折扣。這也意味著我們必須回答諸如:當一顆芯片被集成進售予運營商的系統(tǒng)中時,數(shù)據(jù)的所有權(quán)歸誰?”

結(jié)論

成功部署 SLM 技術(shù)取決于審慎的架構(gòu)決策、清晰的目標,以及對硬件和軟件集成采取靈活的方法。系統(tǒng)架構(gòu)師不僅要評估技術(shù)需求,還必須考慮貫穿硅生命周期的數(shù)據(jù)安全、數(shù)據(jù)所有權(quán)和分析等更廣泛影響。通過優(yōu)先考慮靈活性、標準化和可擴展性,組織能夠從 SLM 中釋放真正的價值,將芯片和系統(tǒng)轉(zhuǎn)變?yōu)橹悄堋f(xié)作的實體,在日益復雜的環(huán)境中推動創(chuàng)新與可靠性。

評論