"晶體振蕩器"的核心技術(shù)

在電子設(shè)備中, 晶體諧振器(簡稱晶體) 如同數(shù)字電路的“心臟”,提供穩(wěn)定、精確的時(shí)鐘信號(hào)。然而,要讓這顆“心臟”可靠地跳動(dòng),并非簡單地將晶體接入電路即可。它需要精妙的振蕩電路配合,并關(guān)注一系列關(guān)鍵參數(shù)。本文將深入淺出地解析晶體的工作原理、核心參數(shù),以及工程師在可靠性應(yīng)用中必須關(guān)注的設(shè)計(jì)要點(diǎn)。

一、晶振是如何“跳動(dòng)”的?——典型工作原理

晶體諧振器本身是一個(gè)無源器件,它需要配合外部的振蕩電路才能產(chǎn)生持續(xù)的電信號(hào)。這與晶體振蕩器(有源器件,內(nèi)部已集成振蕩電路)是本質(zhì)區(qū)別。

1. 振蕩的三大條件

要實(shí)現(xiàn)可靠的持續(xù)振蕩,電路設(shè)計(jì)必須滿足以下三個(gè)核心條件:

2. 典型外圍電路解析

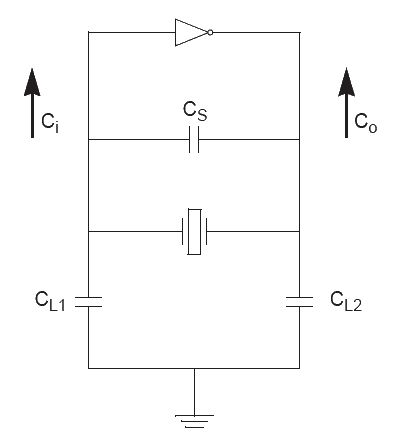

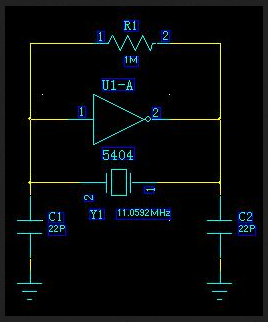

振蕩電路通常由放大電路、正反饋網(wǎng)絡(luò)、選頻網(wǎng)絡(luò)(即晶體)和穩(wěn)幅電路組成。在現(xiàn)代設(shè)計(jì)中,放大電路和正反饋網(wǎng)絡(luò)通常已集成在主IC內(nèi)部。因此,晶體外圍電路的設(shè)計(jì)重點(diǎn)在于穩(wěn)幅電路,以確保安全振蕩和頻率偏差符合要求。

二、掌握核心指標(biāo)——晶體諧振器主要參數(shù)解析

理解晶體的核心參數(shù)是進(jìn)行電路設(shè)計(jì)的基礎(chǔ)。以下是幾個(gè)最重要的參數(shù):

激勵(lì)功率(DL):不可忽視的“能量”

激勵(lì)功率是維持晶體正常起振和穩(wěn)定振蕩所需的能量。設(shè)計(jì)時(shí)必須嚴(yán)格控制:

激勵(lì)功率過小:可能導(dǎo)致晶體無法起振,或信號(hào)雜音比變小,影響短期穩(wěn)定度。

激勵(lì)功率過大:會(huì)導(dǎo)致石英晶片因機(jī)械形變超過彈性限度而引起永久性的頻率變化,甚至可能導(dǎo)致晶片碎裂而停振。

規(guī)格書通常記載的是最大激勵(lì)功率。不同模式的晶體最大激勵(lì)功率參考值如下:

使用者可通過調(diào)節(jié)限制電阻R1和負(fù)載電容C1/C2的值來調(diào)節(jié)實(shí)際的激勵(lì)功率。

三、可靠性設(shè)計(jì)的“生命線”——負(fù)性阻抗(-R)

負(fù)性阻抗(-R)不是晶體的規(guī)格參數(shù),卻是振蕩電路設(shè)計(jì)中最重要的性能指標(biāo)之一。

1. 負(fù)性阻抗的概念

晶體的等效電路中存在一個(gè)振動(dòng)摩擦損耗電阻R(即ESR),它會(huì)消耗振蕩電路的能量。如果能量耗盡,晶體就會(huì)停止振蕩。負(fù)性阻抗(-R)來源于振蕩電路中的放大電路,它是一個(gè)能量源。當(dāng)這個(gè)能量源(-R)大于振蕩電路的損耗(ESR)時(shí),回路才能維持穩(wěn)定振蕩。

2. 核心要求:-R必須足夠大

為了確保晶體電路能夠安全起振和穩(wěn)定振蕩,負(fù)性阻抗必須滿足以下條件:

-R≥3~10倍的ESR

?低于3倍:可能導(dǎo)致晶體不起振、振蕩不穩(wěn)定或啟動(dòng)時(shí)間延長。

?5倍以上:是業(yè)界普遍推薦的安全設(shè)計(jì)裕量,通常消費(fèi)類≥3倍,工控類≥5倍,汽車電子≥10倍。

注意:當(dāng)線路負(fù)載電容值增大或頻率往高頻方向偏時(shí),負(fù)性阻抗會(huì)變小,因此在設(shè)計(jì)時(shí)需要留足裕量。

四、工程師必看——負(fù)載電容(CL)的精細(xì)化設(shè)計(jì)

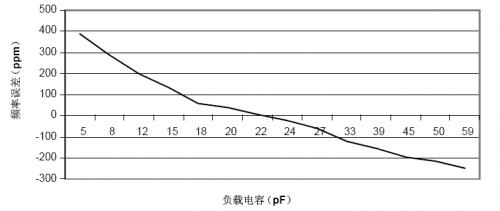

負(fù)載電容的匹配性直接決定了晶體電路的頻率精度。只有當(dāng)電路的負(fù)載電容與晶體規(guī)格書指定的CL一致時(shí),時(shí)鐘信號(hào)的頻率才能與標(biāo)稱值一致。

1. 負(fù)載電容的計(jì)算

電路中的實(shí)際負(fù)載電容CL_actual由外接電容C1、C2和寄生電容Cs共同決定:

其中:

?Cs:包含IC內(nèi)部雜散容值、PCB布線間的電容量、板層間的寄生電容等。一般典型值取 5pF。

?C1/C2:用于調(diào)整電路的負(fù)載電容。

2. CL選擇的三個(gè)關(guān)鍵點(diǎn)

在實(shí)際應(yīng)用中,負(fù)載電容的選用需要注意以下三點(diǎn):

電容要求:C1和C2的值一般要求相等,且要求使用溫度特性好的電容(如NPO材質(zhì)),以保證頻率穩(wěn)定。

精度要求:C1和C2的取值精度要求在10%以內(nèi)。

調(diào)試標(biāo)準(zhǔn):C1和C2的調(diào)試取值,應(yīng)以已知頻偏的晶體部品為參考,而非晶體規(guī)格書中的標(biāo)稱頻率。換言之,取值判斷標(biāo)準(zhǔn)是以所得頻率靠近已知頻偏為佳,而非靠近規(guī)格值的0ppm為佳。

3. 頻率偏差與CL的關(guān)系

當(dāng) CL_actual大于規(guī)格書的CL值時(shí),晶體頻率小于標(biāo)稱頻率。

當(dāng) CL_actual小于規(guī)格書的CL值時(shí),晶體頻率大于標(biāo)稱頻率。

因此,即使標(biāo)稱頻率相同的晶體,如果它們的負(fù)載電容CL不同,也不能貿(mào)然互換,否則會(huì)導(dǎo)致時(shí)鐘頻率偏差過大。

總結(jié)

晶體諧振器的可靠性設(shè)計(jì)是一個(gè)系統(tǒng)工程,它要求工程師不僅要關(guān)注晶體本身的參數(shù),更要關(guān)注外部振蕩電路的性能。通過精確控制負(fù)載電容來保證頻率精度,通過確保負(fù)性阻抗的裕量來保證起振穩(wěn)定性,并通過調(diào)節(jié)激勵(lì)功率來保證晶體的長期可靠性。

評(píng)論