LTspice中的隨機數是真隨機數嗎?

本文討論如何在LTspice仿真中利用flat()、gauss()和mc()函數來實現偽隨機數和真隨機數的生成,并介紹如何使用設置面板的Hacks部分中的 Use the clock to reseed the MC generator(使用時鐘重新設置MC生成器的隨機種子)選項。文章探討了偽隨機數和真隨機數之間的利弊權衡,同時比較了蒙特卡羅統計仿真與更有針對性的最壞情況仿真之間的差異。

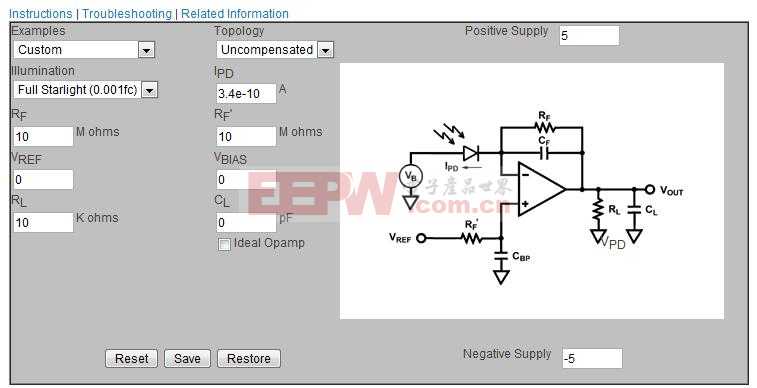

在LTspice?原理圖中,有多種方法可模擬隨機性。LTspice中的flat()、gauss()和mc()函數支持在LTspice仿真中引入隨機性。本文以mc()函數為例,說明如何模擬無源元件值的容差。打開LTspice后,選擇Help > LTspice Help(“幫助”>“LTspice幫助”,或按F1)可打開《幫助手冊》,了解有關flat()和gauss()的更多信息。

圖1中的示例使用mc()來設置R1和C1的標稱值和容差。例如,R1的標稱值為10 kΩ,容差為5%。mc(x,y)函數將生成在x*(1-y)和x*(1+y)之間均勻分布的偽隨機數。請繼續閱讀,深入了解偽隨機數和真隨機數之間的區別,以及如何強制LTspice生成真隨機數。.STEP 指令用于指示LTspice運行仿真的迭代次數。在下面的示例中,.STEP指令以1為增量將一個虛擬參數從1逐步增加到100,從而進行100 次仿真運行,其中R1和C1的值都是隨機生成。

圖1. RC電路使用mc()來設置無源元件的值和容差

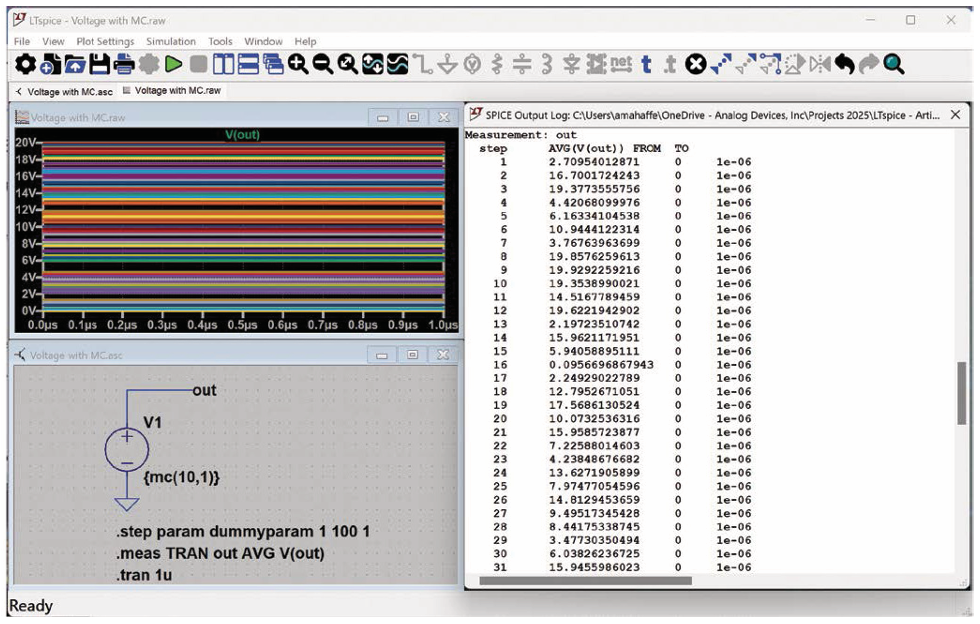

觀察mc()函數在每一步迭代中的行為:圖2顯示了一個僅使用電壓源的簡單示例。此示例使用mc()將標稱電壓設置為10 V,并將容差設置為100%。因此,預計將得到一個在0 V和20 V之間均勻分布的電壓。從波形查看器和SPICE輸出日志中的結果可以看到,在10次迭代中,電壓變化范圍是2.7 V至19.92 V,分布并不完全均勻,但更多次迭代將有助于確保結果在統計上更加合理。

圖2. 電壓源使用mc()生成隨機電壓

我們不妨更仔細地觀察,并反復運行這個仿真。在這些仿真過程中,數值是否發生了變化?在我的計算機上,每次運行仿真時,每一步迭代都得到相同的電壓值。這稱得上“隨機”嗎?

您所看到的是代碼和計算機在生成隨機數時的典型表現。編程語言中的隨機數生成器有一個與之關聯的可選seed()方法。想要獲得真隨機數(即每次運行程序時得到不同的隨機數),需要調用seed()方法,并為其指定動態變化的種子值。通常,程序員會將當前系統時間傳遞給seed()方法來實現這種隨機性。

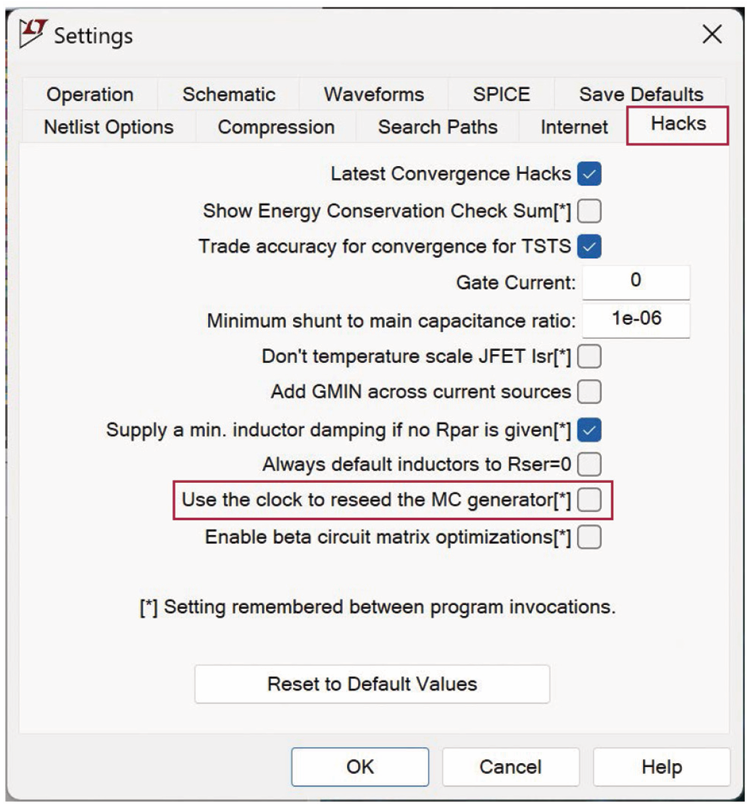

這與我們的LTspice仿真有何關系?如果希望每次運行仿真時獲得不同的隨機值,則必須在設置面板的Hacks部分中啟用 Use the clock to reseed the MC generator 選項(參見圖3)。

圖3. LTspice設置面板的Hacks選項卡,顯示了如何實現真隨機性

此Use the clock to reseed the MC generator選項也適用于flat()和gauss()函數。這些函數可以用在mc()所使用的地方。

不過,請慎重考慮否是需要刻意實現這種仿真行為。您希望仿真過程是真隨機的嗎?倘若如此,您的仿真將失去可預測性和可重復性。

為了說明這一點,讓我們回顧圖2中的示例。如果目標是模擬一個在0 V和20 V之間均勻分布的電壓呢?當前的示例不太符合預期。然而,通過將迭代次數從10次增加到100次,我們可以使仿真結果更接近目標(圖4)。這種調整使得仿真更接近實現預期的分布范圍。

圖4. 使用mc()且迭代更多次數的電壓源

現在有兩點已經很明確:(a) mc()迭代運行100次,便能得到一個相當好的數值分布;(b)如果不啟用reseed the MC generator(重新設置MC生成器的隨機種子)功能,則每次運行仿真將得到可重復的結果。

如果電路中多處使用mc()呢?能否保證通過100次迭代能夠覆蓋所有容差?圖5展現了這一嘗試,其中顯示了兩個使用mc()的電壓源。將V(out1)作為y軸、V(out2)作為x軸進行繪圖,可以清楚地看到,V1和V2的組合呈現出高度隨機的坐標分布(右鍵單擊x軸標題,將x軸從步進虛擬參數更改為V(out2))。但從技術上講,這些電壓的最小值和最大值并非同時達到,導致極端(角落)情況的覆蓋有些不足。

圖5. 繪制一次仿真中兩個mc()電壓的結果

如果目標是接近完全覆蓋,則需要更多次迭代(圖6)。

圖6. 繪制更多次迭代的結果

對于這個簡單的例子,仿真運行速度相當快,即便運行1000次也毫無問題。但如果仿真運行時間很長,運行多次迭代需要數小時或數天時間呢?應考慮啟用 Use the clock to reseed the MC generator選項是否有幫助。如果在一次仿真運行中,mc()生成的值令人滿意,那么接下來的目標是讓這些結果在每次運行時可重復,還是隨機變化呢?啟用此項功能之前,這是一個值得考慮的好問題。

為了大幅縮短仿真時間,我們來看一種相對不太隨機的方法。

圖7所示的例子確保了仿真能夠覆蓋無源元件容差的所有邊緣情況,同時保持總體仿真時間盡可能短。這個例子遍歷了R1的三個值和C1的三個值,進行了九次仿真,并覆蓋了元件值同時達到最小值(或最大值)的情形。

圖7. 設置元件的特定值以模擬容差導致的行為

如果目標是探索電路在極端工況下的行為,則相對不太隨機的方法可能更為合適。相反,如果目標是對仿真在一系列變化下的行為進行統計分析,則使用大量仿真并通過隨機函數引入隨機性可能是更好的方法。但無論哪種情況,您現在應該已經對如何在LTspice仿真中引入(或不引入)隨機性有了更好的理解。

評論