基于DSP的列車應變力測試系統設計方案

摘 要:本文介紹了基于TMS320VC33 DSP芯片的應變力測試系統的設計,給出了結構原理框圖,并圍繞DSP設計了測試系統的中斷、復位子系統、存儲子系統和通信子系統。同時還對測試系統進行了信號完整性分析。

關鍵詞:測試系統;DSP;應變力;信號完整性

車輪與軌道間的作用力是評價車輛運行品質的重要因素,能否準確及時地獲取輪軌間的作用力直接影響著車輛脫軌系數等參數的計算。應變力測試系統是設計列車運行狀態地面安全監測平臺的關鍵環節,本文用DSP芯片開發的測試系統正是針對這一需要。

測試系統硬件設計

系統整體結構

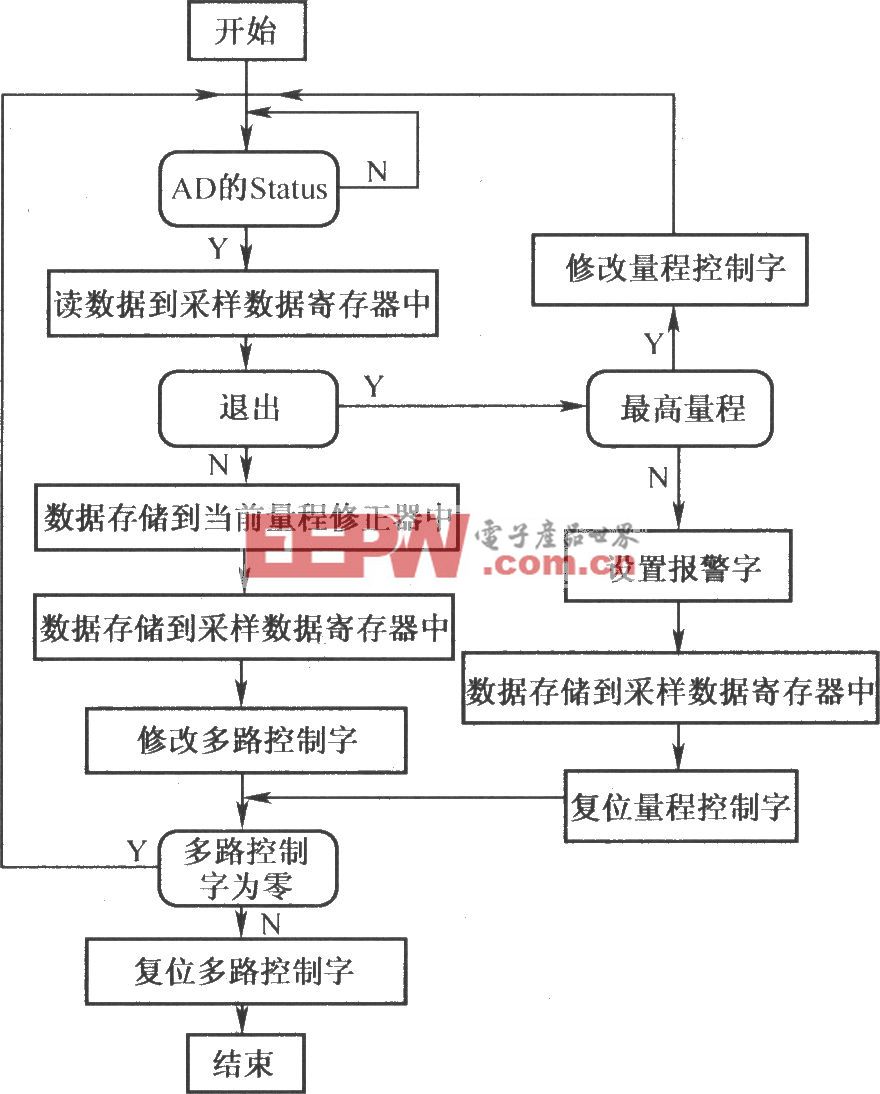

測試系統以高速、高精度的DSP為核心,構成了包括模擬信號預處理、A/D轉換、D/A轉換等環節的實時信號測試處理系統。其原理框圖如圖1所示。

應變傳感器輸出的模擬信號,經RC濾波網絡初步濾去信號中的高頻成分,然后經A/D轉換后,變為數字信號。RC濾波網絡、A/D轉換構成了測試系統的前向通道。

中央處理單元以TMS320VC33為主體,該DSP是一款高精度、大容量、寬功率范圍的浮點處理器,具有高度的并行化,以及DMA協處理器通道。同時,本設計還在系統中設置了1個64K×32位的數據存儲器和512K×8位的程序存儲器,與DSP共同構成了整個系統的存儲系統。

可編程邏輯(CPLD)是測試系統的硬件控制核心。其主要任務是控制A/D轉換、產生存儲系統的片選信號。

中斷、復位子系統不僅起到系統復位的作用,同時還用來確定系統應用程序的位置。DSP根據此系統來裝載應用程序并運行。

中斷、復位子系統設計

在本測試系統中,DSP需要單獨地組成一個系統,因而把TMS320VC33設置為微計算機模式,此時TMS320VC33具有程序引導功能。當系統上電或復位時,TMS320VC33監測4個中斷管腳的狀態,根據BootLoader程序定位表來確定用戶程序的地址,然后運行自身的BootLoader程序把用戶程序下載到指定地址空間。實現系統BootLoader的復位電路如圖2所示。

時鐘電路的設計

TMS320VC33的時鐘,既可由外部提供,也可由板上的振蕩器來提供,但外部時鐘的精確度高、穩定性好、使用方便,因而本設計中使用了12MHz的外部時鐘CLKMD0 CLKMD1=11的時鐘模式,經內部5倍頻后,產生60MHz 的系統時鐘。

總線驅動

由于DSP的地址總線和數據總線的驅動能力有限,當負載較大時,需要用總線驅動對其負載能力進行擴展,以保證系統能穩定工作。本設計選用了TI公司的寬總線16位雙向總線驅動器SN74LVTH16245,它具有很高的集成度和性能。

評論