淺談低電壓低靜態電流LDO的電路設計

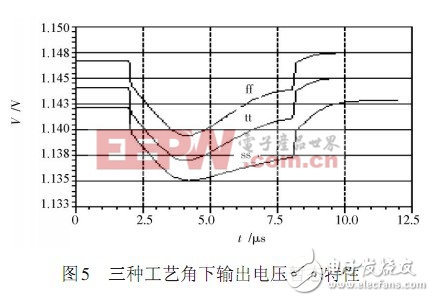

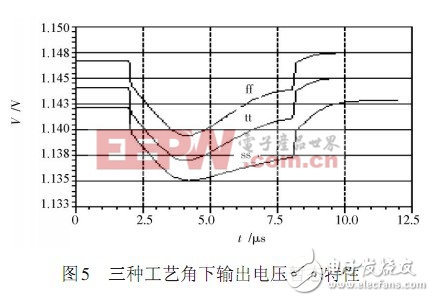

暫態輸出電壓變化如圖5所示,當負載電流從0~30 mA瞬態變化時,輸出電壓變化最大僅為9 mV.

4 結語

本文給出了一種低電壓1.14 V、低靜態電流1.7 μA 的LDO,通過將帶隙基準電壓源與誤差放大器合二為一獲得精簡結構的LDO.

因此實現了低靜態電流消耗,同時獲得較好的暫態輸出電壓性能,最大暫態電壓變化僅為9 mV.

暫態輸出電壓變化如圖5所示,當負載電流從0~30 mA瞬態變化時,輸出電壓變化最大僅為9 mV.

4 結語

本文給出了一種低電壓1.14 V、低靜態電流1.7 μA 的LDO,通過將帶隙基準電壓源與誤差放大器合二為一獲得精簡結構的LDO.

因此實現了低靜態電流消耗,同時獲得較好的暫態輸出電壓性能,最大暫態電壓變化僅為9 mV.

評論