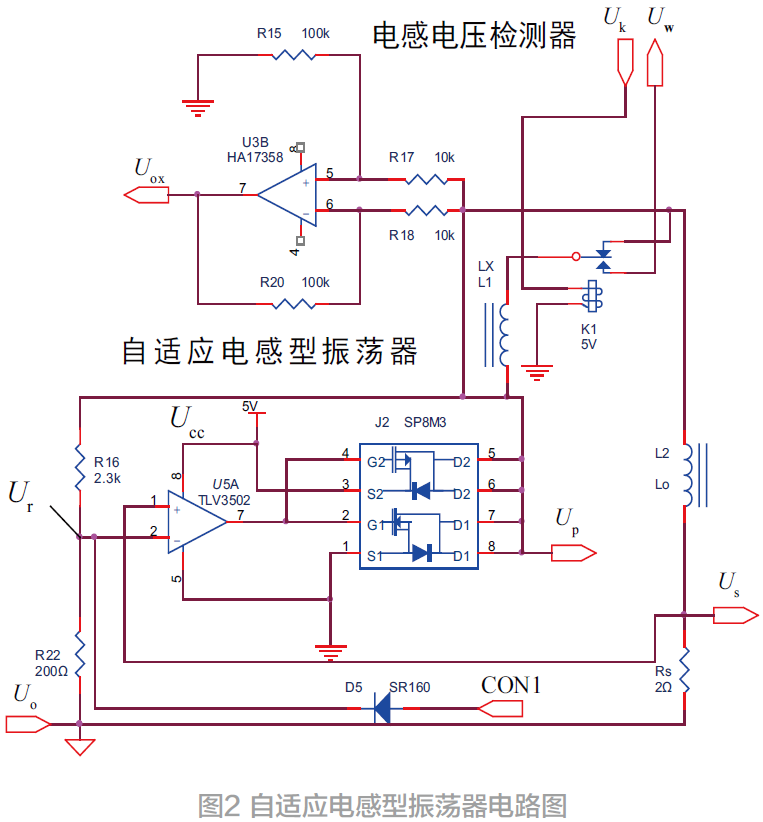

集成運放參數測試儀設計方案

抗干擾措施:

系統要測量信號非常微弱,最小數量級可達PA級,增益高,非常容易受干擾和產生自激。因此抗干擾措施必須做的很好,才能避免自激,減小噪聲,提高測量精確度。通過理論分析和實驗,我們采用下述方法減小干擾,避免自激。

1.將系統測量電路放入屏蔽盒中進行電磁屏蔽,避免空間高頻電磁干擾,和工頻干擾。

2.模數隔離。由于數字電路有非常大的高頻對地干擾,非常容易對模擬電路產生影響。在電路板制作中我們采用了模擬地數字地一點接地。

3.由于主測量電路工作在高增益狀態下,極易產生自激,使得測量無法進行。為消除自激,我們對輔助運放加上相位矯正網絡,在靠近兩運放處對正負供電進行電源去耦。去耦電容采用一大一小:大的選用漏電流較小的钅旦電解電容,小的采用具有優良高頻特性的cbb電容。這些有效的保證了電路的穩定。

4.電源隔離。由于系統要有 供電,其中繼電器的開關噪聲非常大,實際示波器測量可看到瞬間峰值可達1V,我們采用了完全的獨立電源供電,有效減小對主測量電路的影響。

七、結論

基本完成了系統基本及發揮部分的要求,在某些方面性能有極大的提高,大大超過了要求。但由于時間緊張等原因,整個系統還存在著設計簡陋,測量精度不是很高等問題。由于系統采用了模塊化設計,系統還有很大的升級擴展空間。經過進一步的完善,完全可以應用于實際測量中。

參考文獻:

1 電子電路設計與實踐. 姚福安編著. 山東省科學技術出版社.2001

2 MCS-51單片微型計算機原理與接口技術. 東北大學出版社.1994

3 全國大學生電子設計競賽組委會. 第四屆全國大學生電子設計競賽獲獎作品選編.

4 凌陽16位單片機基礎原理與應用. 北航出版社

5 計算機控制系統. 機械工業出版社

6 電子系統設計. 浙江大學出版社

7模擬集成電路應用. 山東大學出版社

8 VHDL數字電路設計應用實踐教程. 機械工業出版社

9 FPGA設計及應用. 西安電子科技大學出版社

10 VC++6.0應用設計及提高 電子工業出版社

評論