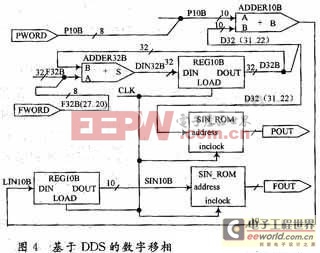

基于AVR和FPGA數字式移相信號發生器的設計

2.3 嵌入式鎖相環的設計

當輸出波形頻率較高時,由于采樣一個完整周期的波形數據點數減少,勢必引起波形失真,要消除波形失真,一是可以增加采樣波形數據的點數,二是提高系統的主工作時鐘頻率。若不增加外配ROM的情況下,可以使用后一種方法。本系統設計時在充分利用FPGA的存儲空間的情況下,為了提高波形的輸出頻率(在不失真的條件下),還使用了Cyclone器件中的嵌入式鎖相環,提高系統的主工作時鐘頻率,在實際工作時的主時鐘頻率達120 MHz。其在QuartusⅡ下的仿真圖如圖5所示。

3 實驗結果

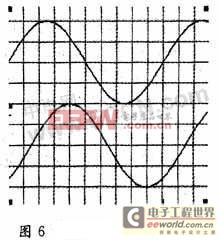

最后D/A輸出的信號經過濾波后得到的信號波形如圖6所示。

4 實驗結論

通過設計和實驗,得出以下結論:

(1)本設計通過鍵盤控制波形輸出的頻率和相位,波形頻率可調范圍為:10 Hz~15 MHz,相位可調范圍為:0°~360°,頻率最小步進值為1.795 15 Hz。

(2)波形失真度與儲存波形ROM的位數及主工作時鐘頻率有關。

(3)使用FPGA中的嵌入式鎖相環或者增加采樣波形數據的點數(此時需要外配置ROM),可以大大提高主工作時鐘的頻率,消除波形失真。采用哪種方法或同時采用兩種方法,取決于實際應用的需要。采用VHDL語言,具有很強的電路描述和建模能力,能從多個層次對數字系統進行建模和描述,從而大大簡化了硬件設計任務,提高了設計效率和可靠性。

(4)基于FPGA和VHDL的在系統可重編程的特點,系統更新只需修改VHDL程序即可,無需重新制作系統。外圍電路數/模轉換器的控制也可由VHDL程序實現,因此數/模轉換芯片更換方便。

(5)采用ATmega16單片機,可實現在線編程,方便靈活,提高了開發效率,同時采用串行數據傳送方式占用口線少,減少了資源的浪費。

(6)本設計中的DDS電路與專用DDS集成芯片相比,其靈活性更好,可生成任意波形,頻率分辨率高,轉換速度快,穩定性好,精度高,且均可對頻率、相位、幅度實現程控,更重要的是,他如果作為IP核將具有更大的可移植性。

評論