基于ARM內(nèi)核SoC的FPGA 驗證環(huán)境設計方法

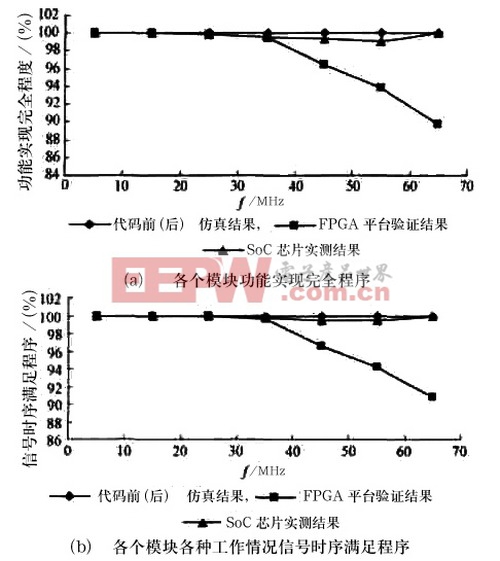

圖9 代碼仿真、FPG平臺驗證及SoC芯片實測結(jié)果比較

結(jié)束語

本文提出了一種常用的基于ARM內(nèi)核SoC 的FPGA 驗證環(huán)境的設計方法,并給出了電路結(jié)構(gòu)框圖和相應的外圍電路設計。根據(jù)該設計, 在FPGA 內(nèi)實現(xiàn)AMBA 總線、存儲器接口和中斷控制器,加上外面的ARM處理器核,構(gòu)成了ARM SoC 的最小系統(tǒng),根據(jù)具體目標系統(tǒng)的需要,可以增加LCD 控制器、AC97 控制器、USB 控制器等模塊,構(gòu)成一個非常實用的驗證平臺。在IP 核燒入后,可以使用ARM ADS(ARM Developer Suite) 軟件開發(fā)工具,在線對設計的硬件電路、硬件驅(qū)動軟件、操作系統(tǒng)和高層應用軟件進行調(diào)試,從而大大縮短了基于SoC 芯片的應用系統(tǒng)的開發(fā)時間。隨著FPGA 的飛速發(fā)展,用戶可以選用更加先進和方便使用的FPGA ,還可選用內(nèi)嵌ARM 核的FPGA 芯片來構(gòu)建驗證平臺。同時,該系統(tǒng)在電壓設計、模塊選用甚至處理器核的選用方面都考慮了升級擴展技術,可供其他SoC 的驗證借鑒。

評論