基于FPGA的數據中繼器設計

4 測試與分析

高速數據中繼器設計制板完成后,還要將其置于整個路由器環境中進行性能測試,其測試結構如圖三所示,最下面四個模塊組成了高速數據中繼器。

圖 三:測試結構圖

從圖中可以看出,測試時需要兩個10GbE接口,一個用于接收測試儀的數據報文,另外一個則是對經過轉發處理和端口交換后的數據報進行處理后返回給測試儀進行分析。下面給出衡量系統性能的關鍵參數的測試情況。

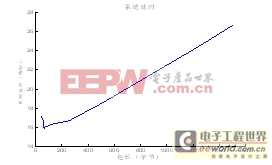

測試中選用的數據包長是46、60、64、65、128、256、512、1024、1280、1508,測試時間是1分鐘,測試結果如下:

圖 四:系統時延測試曲線圖

由于我們的中繼器設計時的性能指標是可以達到10Gbps速率下40字節IP包的處理能力,在測試儀的吞吐量下不應該丟包,實際測試結構在上述10種包長的情況下,IPv4和IPv6的單播、組播包的丟包率均為0。系統時延測試結果如圖四所示。從測試結果可以看出,高速數據中繼器應用在高速路由器中后完全滿足高速路由器對數據中繼要求的各項性能指標。

5 創新點總結

本文的創新點是提出了一種基于FPGA的高速數據中繼器設計方案,并綜合分析了ASIC和NP等方法設計的高速網絡中繼器設計方法,在設計的功能和靈活性兩方面做了很好的權衡。從測試結果可以看出,本文設計很好地滿足了網絡處理的基本功能以及高速數據中繼的性能指標要求。

評論