基于FPGA的卷積碼的編/譯碼器設計

3 譯碼器設計與實現

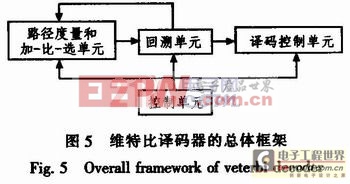

維特比譯碼器包括4個子模塊,如圖5所示。

1)控制單元 向各個功能模塊提供控制信號,保證譯碼器的工作時序正確,協調各個功能模塊從而促使整個譯碼器的正常工作。

2)路徑度量和“加-比-選單元”計算和比較每條支路的路徑度量,得到并保存剩余路徑提供給回溯單元。對于(2,1,3)卷積碼,譯碼深度D=5(m+1)=20,為保證存儲單元和回溯單元同時并行工作,存儲單元為2D(m+1)2m=1280 bit。

3)回溯單元 從前面“加-比-選”電路送來的剩余路徑中選擇量度最小的剩余路徑,從這條路徑對應的狀態開始向前尋找,直到找完前面所有狀態,并從存儲單元中讀出譯碼信息送給譯碼控制單元。

4)譯碼控制單元 將回溯單元送來的譯碼序列反轉順序輸出即為所要輸出的正確的接收序列。其中反轉順序的操作可由RAM實現,順序寫入倒序讀出。

4 譯碼器設計中改進和優化算法

本文采取狀態路徑和判決比特同時存儲,在表示狀態信息的比特前加上1位判決比特來表示相應狀態的輸入支路的譯碼信息,因此,譯碼器在回溯時就可直接輸出判決比特作為譯碼器的輸出,降低了譯碼器的判決難度,節省了存儲回溯路徑所需要的內存,從而降低了譯碼器結構復雜性。

本設計中譯碼器在計算所有狀態的路徑量度的同時進行路徑存儲,從而大大提高了譯碼速度。路徑量度是指每個狀態的2條輸入支路和2條輸出支路,路徑存儲指的是狀態存儲以及相應的譯碼判決比特存儲。該結構的譯碼器對每一個狀態都具有獨立的處理單元,彼此互補影響,并行工作,提高了譯碼速度。對于(2,1,3)卷積碼,一個時鐘需要進行2x2x2m=32次路徑量度計算和2m=8次4比特存儲操作。充分發揮了FPGA擁有大量LCS和RAM的優勢。

在網格圖中,隨著狀態的改變,每個狀態的輸出支路的路徑量度逐漸增加,造成存儲資源壓力增大,設計中在每次進行路徑量度計算時,將該狀態的量度值與上次剩余路徑量度的最小值做差后進行保存,以達到減小存儲器空間的需求。對于編碼效率為1/2的卷積碼,以上差值最大不超過2m,因此,路徑量度的量化寬的為1b(2m)。對于(2,1,3)卷積碼,存儲路徑量度的寄存器位寬為lb(2×3)=3。

評論