一種基于FPGA的語音錄制與回放系統的設計

1.3語音采集模塊

語音采集單元頂層綜合模塊如圖4所示。系統通過語音采集模塊將語音芯片采集的聲音數據串/并轉換為16位PCM碼,聲音數據傳送至S-RAM存儲器內保存,這里設置了4s錄音時間,用戶1次輸入3個孤立詞(如數字),4×8KB=32KB,考慮到32KB的原始數據需要預處理、FIR濾波和歸一化。斷點檢測,所有處理后的數據仍然存入后續的SRAM地址中。檢測出的孤立詞分別存入獨立首地址后面。

1.4語音采集實時采樣

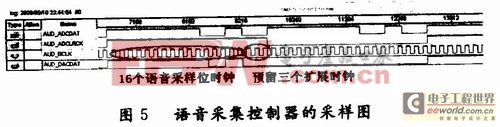

鎖相環PLL給予WM8731工作在18.4MHz時鐘頻率下,通過I2C總線控制器設置WM8731工作在8kHz的采樣頻率下。圖5為在嵌入式邏輯分析儀(SignalTapⅡLogicAnalyzer)下語音采集控制器的采樣圖。

圖5為實時采集圖,測試人現場讀入語音數據,模塊實時進行語音采集回放。從圖中可見,左對齊語音采集過程一共有19個脈沖,其中前16個脈沖為有效語音數據提取脈沖,后3個脈沖為將來處理擴展預留。有效語音提取出來之后便存人SRAM中。該模塊通過計數器,從啟動錄音開始,自動錄制4s的語音信號。

2語音錄制回放仿真

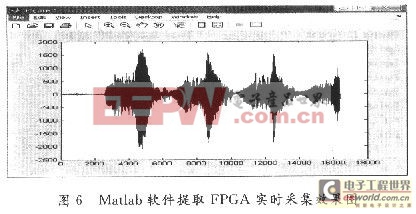

經WM8731采集的語音信號轉換并存儲于SRAM,然后用SRAM中的數據將SRAM的語音數據導出,圖6為語音采集模塊處理后作者錄入的數字符號“1234”效果圖。

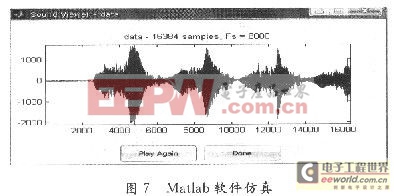

圖6是通過DE2控制面板軟件讀取SRAM前256KB數據(地址:O~0x1FFFF)在Matlab軟件上畫出來的圖形,同時為了對比,通過Matlab自帶的[y,fs,bits]=wavread(‘Blip’,[N1N2]),進行同樣話語的錄制,用sound(x,fs,bits)對聲音進行回放,仿真結果見圖6、圖7。從仿真圖可看出,以Matlab平臺為標準,FPGA實時采集與現實吻合。

3結語

該系統充分利用了FPGA的高速處理能力,自行設計采集模塊和I2C協議驅動模塊,并通過AWALON總線掛載在Nios軟核上,很好地實現了實時高速采集回放,充分體現了FPGA的優越性能。同時結合SoPC設計理念,使系統一片式整合。

評論