一種基于FPGA和單片機的掃頻儀研究與設計

3 系統軟件設計

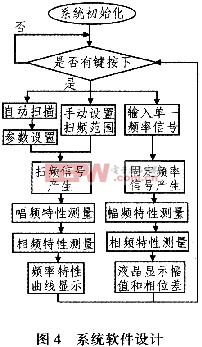

系統軟件設計由單片機和FPGA組成。整個系統以用戶按鍵中斷為主線,調用不同的處理函數,與FPGA中各個控制模塊之間,以總線的進行數據的交換,實現了系統測量頻率特性的功能。軟件流程圖見圖4。

4 結束語

本掃頻儀利用數字頻率合成技術(DDS)產生掃頻信號,通過14位D/A轉換器DAC904產生了10 Hz~100 kHz的正弦掃頻信號,作用于被測網絡。網絡的輸出信號通過有效值采樣電路,以及由比較器LM311配合FPGA內部實現的測相電路,完成了對被測網絡頻率特性的測量。

為對系統的性能進行測試,制作了一個中心頻率為5 kHz。帶寬為±50 Hz的阻容雙T網絡。測試結果表明,在網絡的通帶和阻帶內,相頻特性測量均達到了3°以內的測量精度,幅頻特性的測量誤差均小于50%。此外,該系統可以通過鍵盤輸入掃頻范圍,通過示波器顯示幅頻、相頻曲線,并可以在液晶顯示器上顯示該網絡在特定頻率點上的幅度、相位特性值。該系統操作簡單,成本低廉,測量精確,具有很強的實用性。

評論