一種基于PXI的高速數字化儀模塊的設計應用

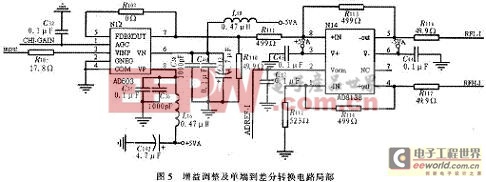

本設計中。A/D轉換器選用Mamix公司的MAXl215,該芯片是一款12 bit/250 Ms/s的高速A/D轉換器,它具有出色的SNR和SFDR特性,使用250 MHz差分采樣時鐘,接收差分輸入信號,輸出12位LVDS格式的差分數字信號,提供差分同步時鐘信號。為了提高測試精度,單端的輸入信號需要轉換成差分模式后再送入A/D,增益調整及單端到差分轉換電路的局部如圖5所示。考慮阻抗匹配問題,在單端信號轉換為差分模式時,需要在2個差分線上串聯50 Ω的匹配電阻,作為LVDS信號的發送端。

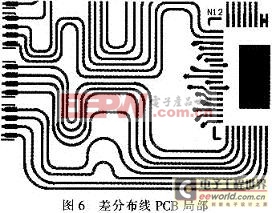

在PCB的設計中,對差分線要進行特別處理。差分線在走線區間內的實際布線公差應控制在5 mil內;差分對內兩條線之間的距離應盡可能小,以使外部干擾為共模特征;要保證每個差分對內的長度相互匹配,以減少信號扭曲;采用電源層作為差分線的信號回路,因為電源平面有最小的傳輸阻抗,可以有效減少噪聲影響。圖6所示為本設計PCB的局部。

本設計中FPGA作為LVDS信號的接收端,首先需要將A/D輸入的LVDS差分數據和同步時鐘信號轉換成單信號。此處選用了xilinx公司的VirtexⅡ-Pro系列FPGA,該系列的FPGA嵌入了高速I/O接口,能實現超高帶寬的系統芯片設計,支持LVDS、LVPECL等多種差分接口,適應性很強,為高速數據接口提供了完善的解決方案。LVDS差分信號的接收可以通過例化IBUFDS_LVDS這個模塊來實現,同時在程序中設置使用內部的匹配電阻,實現LVDS的阻抗匹配。差分時鐘信號由全局時鐘輸入腳接入FPGA,然后通過調用xFPGA特有的數字時鐘管理模塊(DCM),將時鐘轉換成單信號并進行分頻、移相等處理,作為后續處理的時鐘信號。

2.3 PXI接口設計

PXI是PCI在儀器領域的擴展(PCI eXtensions for Instrumenta

評論