約束設置與邏輯綜合在SoC設計中的應用

3.3.2 多時鐘域約束

時序檢查默認以一個時鐘周期為界,但對于ZSU32系統芯片,存在著一些多周期路徑,在這些路徑上,數據不需要在單時鐘周期內到達終點。例如,clk30mhz和clk10mhz是同源的同步時鐘,前者頻率是后者的3倍,對從clk10mhz時鐘域向clk30mhz時鐘域傳輸數據的路徑,采用如下命令:

#按照3個周期(clk30mhz)進行

#建立時間約束

set_multicycle_path 3 -setup -start

-from clk10mhz -to clk30mhz;

對于異步時鐘域之間的路徑,不用進行同步的時序檢驗,應該將其定義為偽路徑(false path),這樣在邏輯綜合時就不必浪費資源去優化。

#將異步時鐘e_clk和p_clk 之間的路徑設置為偽路徑

set_false_path -from e_clk –to p_clk;

set_false_path -from p_clk -to e_clk;

3.3.3 時鐘偏移

芯片中時鐘經過不同的傳輸路徑,由于每條路經延時不一,導致從時鐘源到達各個寄存器的始終輸入端的相位差。這種由于空間分布而產生的偏差叫做時鐘傾斜(clock skew)。此外,由于溫漂、電子漂移的隨機性,使時鐘信號的邊沿可能超前也可能滯后。這種具有時間不確定性的偏移稱為時鐘抖動(clock jitter)。偏移導致時鐘信號到達各個觸發器的時鐘引腳的時間不一致,需要給予約束。

#設置時鐘偏移為0.4 ns

set_clock_uncertainty 0.4 [all_clocks];

3.4 端口約束

SoC芯片通過大量輸入和輸出端口與外界進行信息的傳輸,端口約束主要用于約束頂層端口相連的片內組合邏輯,包括確定輸入延時、輸出延時、輸出負載、輸出扇出負載、輸入信號躍遷時間等。

3.4.1 端口延時

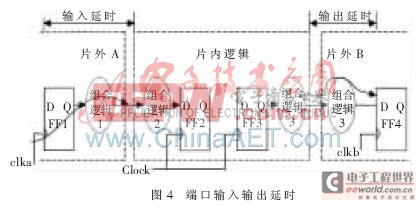

輸入延時是指外部邏輯到電路輸入端口的路徑延時。輸出延時是指輸出端口到外部寄存器的路徑延時。圖4是輸入輸出延時示意圖。

設置范例如下:

#設置端口pci_ad13的輸入延時為4.8 ns

set_input_delay 4.8 -clock clk_main

[get_ports {pci_ad13}];

#設置端口pci_ad16的輸出延時為3.6 ns

set_output_delay 3.6 -clock clk_main

[get_ports{pci_ad16};

評論