基于FPGA的寬帶數字接收機變帶寬數字下變頻器

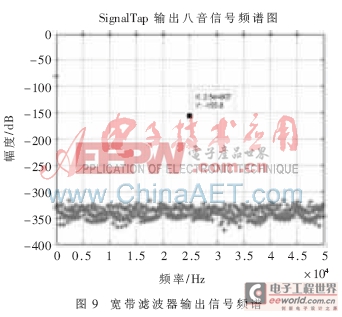

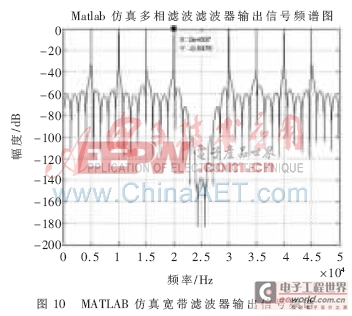

將采樣率100 MHz、帶寬40 MHz的八音信號輸入VB-DDC系統。VB-DDC配置成寬帶多相濾波器濾波,將硬件調試輸出I_out_F、Q_out_F導入MATLAB進行頻域分析如圖9所示,其與圖10的MATLAB理論仿真結果對比,可得設計滿足要求。

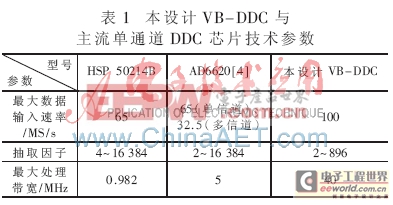

本文基于FPGA芯片Stratix II EP2S60F672C4設計了一個適用于寬帶數字接收機的VB-DDC。該VB-DDC可根據處理信號帶寬要求,靈活選擇下變頻器結構為傳統結構的窄帶DDC或者基于多相濾波結構的寬帶DDC,也可以聯合使用兩種結構。表1列出了本設計VB-DDC與Intersil公司、ADI公司的兩種單通道DDC芯片產品的主要技術參數,其中HSP50214B為目前各種單通道DDC產品中功能最強的型號。本設計的VB-DDC在最大數據輸入率和最大處理帶寬這兩項最重要的性能指標上占有很大優勢。本設計的VB-DDC已經應用于寬帶數字接收機系統。

參考文獻

[1] Intersil.HSP50214B Data Sheet.2000,5.

[2] ANALOG DEVICES.AD6645 Data Sheet.2006.

[3] San Jose. Phase-locked loops reconfiguration(ALTPLL_RECONFIG) megafunction user guide. Altera Corporation,2008,7.

[4] ANALOG DEVICES. AD6620 Data Sheet.1998.

評論