基于CPLD器件的單穩態脈沖展寬電路的設計

2 基于CPLD器件脈沖展寬電路的特點

從上面的電路原理圖和時序仿真波形圖可以看出,利用isp器件構成的脈沖展寬電路具有如下特點:

(1)對輸入脈沖信號的寬度適應能力較強。最窄可以到ns量級,因其僅與所采用的CPLD器件的工作速度有關。因此,特別適用于對窄脈沖雷達信號進行展寬。

(2)展寬脈沖的寬度可以根據需要任意設定,亦可改變電路(例如與單片機相結合)使其做到現場實時自動加載。

(3)展寬脈沖的寬度穩定、準確。因無外接R、C定時元器件,其脈沖寬度僅與所采用的時鐘頻率和CPLD器件的性能有關。

(4)展寬脈沖的前沿與輸入窄脈沖的前沿之間的延遲時間基本恒定,即這個延遲時間是信號從D1的時鐘輸入端到D1的輸出端Q的延遲時間。

(5)電路調試簡單。當需要調整展寬脈沖的寬度時,不需更換元器件,只要將重新設計、仿真通過后的JED熔絲圖文件,通過加載電纜適時加載到CPLD器件內即可。這在對電路進行高、低溫等例行試驗時變得極為簡單、方便和高效。

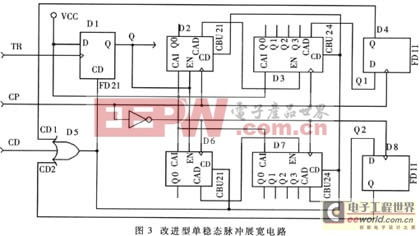

從圖1還可以看出,這種單穩態脈沖展寬電路產生的脈寬精度是小于"+"或"-"一個CP時鐘周期。若要提高展寬脈沖寬度的精度,可以采用圖3所示的改進型單穩態脈沖展寬電路,即在圖1電路的基礎上,將進入isp器件的時鐘脈沖信號經反相器反相后,作為另一個相同脈寬控制電路的計數器的時鐘脈沖。

評論