4 系統仿真及結果

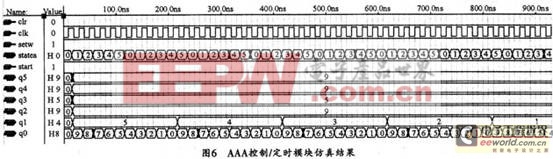

圖6所示是對AAA控制/定時模塊的仿真結果。由此結果可見,當setw置“1”時,statea位選從0到5循環,分別代表六個數碼管的位置。當start置“1”時,q5-q0進行借位減法。q5、q4表示小時,最高可到99小時;q3、q2表示分鐘,最高59分鐘;q1、q0表示秒,最高為59秒。

5 結束語

本設計從總體要求出發,采用模塊化設計方法,實現了長達99小時的定時設計。同時采用QuartusⅡ4.0仿真環境進行了仿真。結果證明,本系統可以實現理想的定時操作而且設計體現了人性化,具有較強的實際應用價值。

評論