基于FPGA的K9F4G08 Flash控制器設計

2.3 讀寫匹配

如果遇到壞塊,會造成讀寫失敗,為了滿足大批量數據讀寫的連續性,在讀寫數據之前必須對當前塊地址進行匹配,這些工作由controller_4G08完成,當主狀態機給controller_4G08發送塊地址后就會執行。

Flash讀寫是對頁操作的,一次2 KB。FPGA中有一個4 KB的ram:ram_4096,用來作為緩沖區存放數據。當需要向Flash中寫入數據時,主狀態機向controller_4G08發Page_program指令,發送5 B地址,controller_4G08會自動進行塊地址匹配,匹配完之后會給主狀態機一個中斷信號,主狀態機收到這個信號便開始將ram_4096中的數據發給controller_4G08,之后等待中斷,收到中斷說明寫指令執行成功。

當需要讀取數據時,主狀態機向controller_4G08發Page_read指令,發送5字節地址,controller_4G08會自動進行塊地址匹配及Flash的頁讀操作,等中斷一到便開始接收來自controller_4G08的數據并存至ram_4096中。

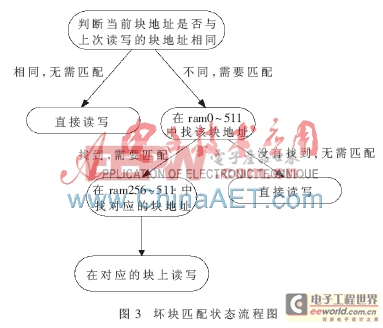

controller_4G08中有一個存放上次塊地址的寄存器,每次進行讀寫操作時,會將當前塊地址與上次的塊地址進行比較,若相同則說明是好塊,可以讀寫;若不同則需要進行匹配。狀態機會從ram_512中尋找該塊是否為壞塊,進行一系列處理。與擦除指令一樣,當讀寫操作遇到新的壞塊時,也會向系統報錯。匹配流程圖如圖3所示。

3 controller_4G08主狀態機

圖4是主狀態機的狀態轉換圖,系統上電復位后,主狀態機將進入等待使能信號狀態。收到使能信號后,主狀態機會從cmd_code_4G08中讀取操作碼,然后啟動對應的子狀態機,執行對應的操作。子狀態機執行完畢以后就會通過int_ctl_4G08發送給主狀態機一個中斷信號,同時將執行結果返回。主狀態機收到中斷信號后,又進入空閑狀態等待下一個使能信號。這樣設計的主狀態機隨時都可以添加新的指令,可擴展性強[4-5]。

評論