基于Nios Ⅱ軟核系統的電能質量監測系統設計

2 電能質量檢測系統硬件設計

2.1 A/D轉換器

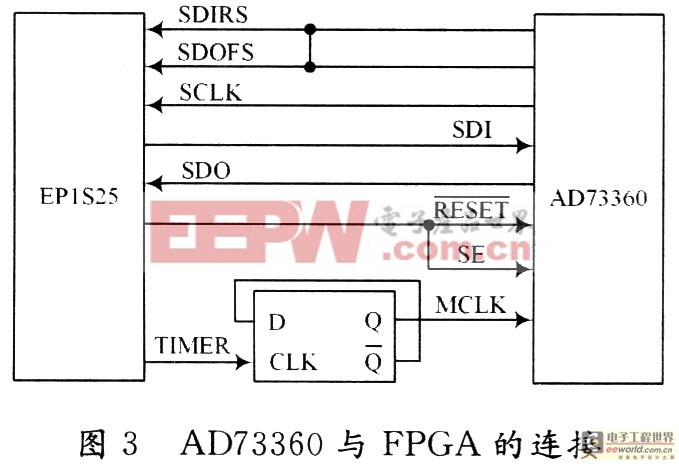

根據實測數據,如果采用12位分辨率的A/D轉換芯片,對15次諧波而言至少會引起1.67%的誤差,而在實際諧波測量中一般測到30次或更多次諧波,因此現場監測單元中A/D轉換器的分辨率應保證為14位或14位以上。本文采用AD73360作為采樣系統的模數轉換芯片。它的六路輸入通道可被分為三對,以分別對應電力系統中的三相。該芯片可以8 kHz,16 kHz,32 kHz,64 kHz的采樣速率同時進行六通道的信號采樣。AD73360可滿足裝置對高速采樣的要求。AD73360與FPGA的連接如圖3所示。

2.2 NiosⅡ軟核處理器

基于32位RISC嵌入式軟核NiosⅡ的SoPC,有著其他SoPC(如基于FPGA嵌入式IP硬核SoPC)不可比擬的優勢。采用NiosⅡ軟核處理器,用戶將不會局限于一般的處理器技術而是根據自己的標準裁剪和定制處理器,按照需要選擇合適的外設、存儲器和接口,輕松集成自己專有的功能,比如DSP、用戶邏輯等。這非常有利于設計高次諧波這種計算量大且控制邏輯復雜的系統。

為了滿足今后的性能要求,該電能質量監測系統應能隨時被改進升級。可以加入多個NiosⅡCPU、定制指令集、硬件加速器等,以達到更好的性能目標。還可以通過Avalon交換架構調整系統性能,該架構支持多種并行數據通道可實現大吞吐量的應用。

2.3 硬件系統平臺設計

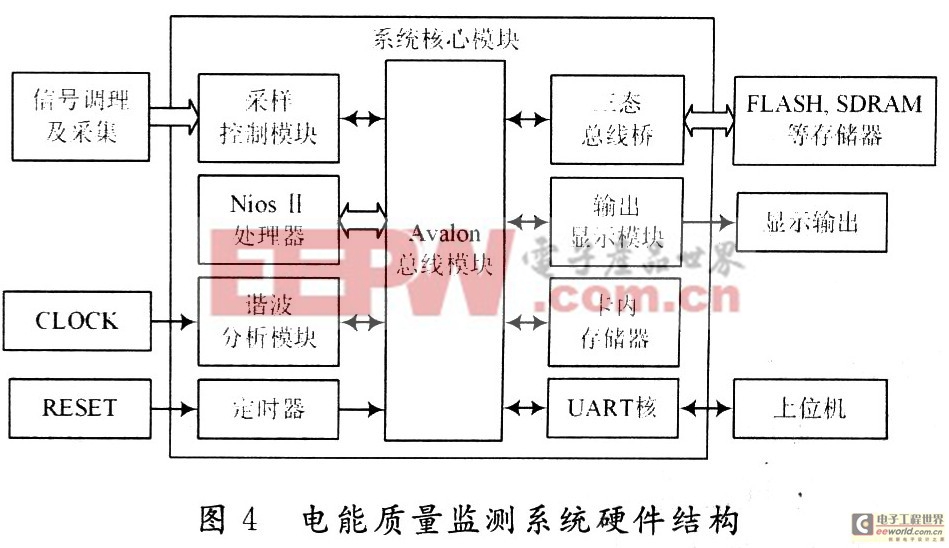

圖4是整個系統的硬件結構框圖。系統組成主要包括:

(1)系統核心模塊采用STRATIX系列的EPlS25型的FPGA,它包含:10個DSP模塊、25 660個邏輯單元、48個嵌入式乘法器、RAM總量高達1 922 576 b,6個數字鎖相環、可用的I/O口最多達到702個。它是一款采用高性能結構體系的PLD器件,結合了強大內核性能,大存儲器,DSP功能,高速I/O和模塊化設計。其內嵌的DSP模塊,提供了高于DSP處理器的數據處理能力,可以完成較為耗費資源的乘法器單元。這些資源對一個電能質量監測系統來說是已經綽綽有余。

評論