采用FPGA設計SDH光傳輸系統設備時鐘

系統時鐘工作在自由振蕩模式時,由高頻時鐘直接自由分頻得到系統時鐘。

根據ITU-T G.813建議要求,SEC帶寬較窄(-3db帶寬在1~10Hz內)。在邏輯濾波器模塊,采用FPGA內部的數字邏輯實現二階線性濾波器,滿足了SEC噪聲傳遞特性的要求。為了靈活應用,濾波器的環路帶寬可以通過微處理器接口進行靈活調整。當參考源切換時,通過濾波器的平滑設計,保證了頻率控制字緩慢變化,可靠地實現了參考源的平滑切換。

數控時鐘產生器模塊由高頻時鐘在頻率控制字的作用下進行受控分頻得到。為了減小數控時鐘產生器輸出時鐘在受控分頻過程中產生的數字相位噪聲,TSP8500芯片設計時采用了獨特的“微小相位調整技術”,使數控時鐘產生器輸出時鐘的Cycle-Cycle抖動僅0.4ns。

SEC一般都采用主備備份設計。由于SEC本身的帶寬較窄,俘獲速度較慢,當主備SEC跟蹤同一路參考源時,無法時刻保持主備SEC相位同步。設計中增加了主備互鎖模塊,保證了主備相位的快速同步。主備互鎖模塊也由ADPLL實現,但其環路帶寬設計的較寬,俘獲速度很快,足以保證主備相位準確同步。SEC工作在主模式時,主備互鎖模塊直接鎖定本板的全數字鎖相環ADPLL輸出的時鐘;而當SEC工作在備模式時,主備互鎖模塊鎖定對板送來的系統時鐘RDSYSCLK。

主備互鎖模塊輸出的時鐘,仍然有0.4ns的相位抖動。在這里通過FPGA自帶的PLL(鎖相環2)進行相位平滑。

主板的系統幀頭直接由主板的38.88MHz時鐘自由分頻得到。而備板的系統幀頭,則由本板的系統時鐘在主板送來的同步幀頭受控下分頻產生。由于主備系統時鐘的相位同步了,所以保證了系統幀頭的相位同步。

1.2 外同步時鐘的設計實現

芯片輸出的外同步時鐘ext_clk_out由一路ADPLL實現。

外同步時鐘可以從輸入時鐘或系統時鐘中任選一路作為參考時鐘進行跟蹤;通過

外同步時鐘環路的濾波設計,也由FPGA內部的數字邏輯直接實現,但是環路帶寬設計得比較寬。當進行參考源切換時,ADPLL會短暫地進入保持工作模式,保證了輸出時鐘的穩定。

由于外時鐘頻率為2.048MHz,不能由311.04MHz時鐘整數分頻得到,所以數控時鐘產生器模塊采用了小數受控分頻設計。由于采用了小數分頻,數控時鐘產生器輸出的外同步時鐘的相位抖動為0.8ns。

鑒于FPGA的PLL資源限制,外同步時鐘沒有采用APLL進行濾抖,而是直接由數控時鐘產生器輸出。但是輸出時鐘的相位抖動也遠遠能夠滿足小于0.05UI的要求。

2 輸出時鐘的性能指標測試

對TSP8500芯片輸出的系統時鐘和外同步時鐘的各項指標進行了測試。下面主要給出時鐘的抖動特性以及鎖定模式下SEC的相位漂移特性和保持模式下SEC的相位漂移特性。

2.1 輸出時鐘抖動特性

將高速示波器設置為“長余暉”模式,測試TSP8500輸出的系統時鐘sysclkout和外同步時鐘ext_clkout的信號波形,得到輸出時鐘的P-P抖動特性。其中sysclkout時鐘的P-P抖動小于100ps;ext_clkout時鐘的P-P抖動小于2ns。

2.2 SEC的相位漂移特性

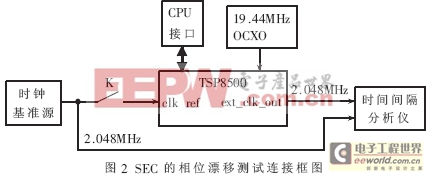

測試方法如圖2所示。

評論