一種基于FPGA/DSP的靈巧干擾平臺設計與實現

引 言

目前,通信干擾的手段以信號大功率壓制為主,本質上屬于物理層能量干擾,存在效費比低,且容易暴露自身目標等缺點,而且隨著新的功率控制和信號處理技術的應用,通信大功率壓制干擾手段的應用遇到了瓶頸。大功率壓制干擾手段的局限性對研究一種新的小功率靈巧干擾技術提出了迫切的需求。美國通信干擾專家Richard A.Poisel于2002年首先提出了靈巧干擾(smart jamming)的概念。他指出可以利用接收機在捕獲輸入信號時間和幀同步信息的過程實施攻擊,這可以看作是靈巧干擾技術的雛形。當前靈巧干擾正成為國內外研究的熱點。本文設計的靈巧干擾硬件平臺正是基于這種背景,可以為靈巧干擾技術的發展提供硬件平臺支持。

1 靈巧干擾平臺工作原理

經過前端射頻選頻濾波和下變頻后,靈巧干擾平臺將獲得所測頻段范圍的中頻信號送入高速信號處理平.臺。高速信號處理平臺由數/模

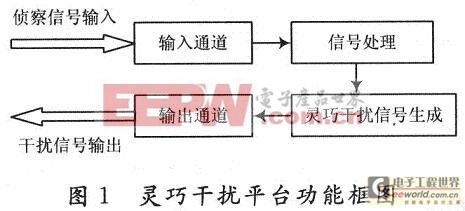

平臺功能框圖如圖1所示。

其中,輸入通道功能包括:A/D變換、數字下變頻;信號處理功能主要有:信號載頻估計、參數估計、調制識別、解調、編碼識別等;靈巧干擾信號生成單元根據信號處理單元得到的信號參數生成干擾信號;輸出通道與輸入通道對應,將產生的干擾信號變換到相應的中頻發出。

2 平臺總體設計

2.1 平臺硬件結構設計

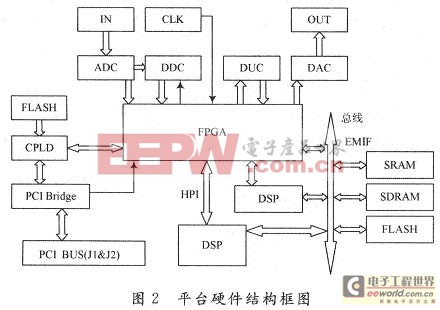

通信偵察信號分析屬于非合作通信環境下的信號處理,其寬頻帶、多調制方式、多信號的特點要求信號處理平臺中的處理器具有高性能的處理能力外,還應具備較強的通用性、靈活性。隨著大規模可編程器件的發展,采用

根據靈巧干擾平臺功能要求,平臺硬件結構如圖2所示。

評論