采用CPLD來替代微處理器的6種方法

脈沖寬度調制

一般而言,設計人員針對某一功能選擇一款微控制器,例如脈沖寬度調制(PWM),這些功能也可以采用CPLD來實現。在PWM中,方波的時間周期不變,而信號保持高電平的時間在變化或者受到調制。這樣,信號的占空比(tON)是變化的。PWM為數字系統中的

CPLD并沒有專用PWM電路,但是實現PWM輸出并不難。例如,MAX IIZ CPLD的內部振蕩器可以用作頻率源,計數器可以用于調制所產生的頻率。

模數轉換器

設計人員經常選擇微控制器來實現模數轉換器(

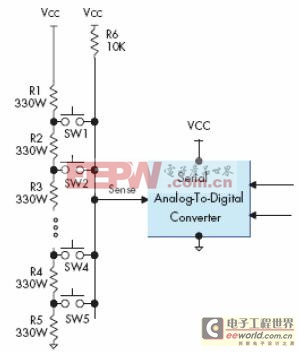

圖2所示為一個基本開關陣列和ADC。在VCC和GND之間串聯了一組電阻,每個電阻抽頭和公共極上連接了一個開關。如果開關接通,電路產生一個和電阻堆中開關位置成比例的電壓信號。要在數字系統中使用,模擬信號必須轉換為數字值,通常選用含有內置ADC的微控制器來實現這一功能。

圖2.模擬鍵盤陣列

然而,CPLD也是一種選擇。加入一個簡單的低成本外部電容后,MAX IIZ CPLD可以利用其內部振蕩器、施密特觸發器I/O以及高密度算法可編程邏輯架構來完成模數轉換(1)。

上電排序

MAX IIZ器件針對大量的系統管理功能進行了優化,例如多電壓系統上電和系統復位上電排序功能,以及片選信號生成等。這兩類應用一般集成在一個非易失、瞬時接通器件中。多電壓系統上電排序功能需要采用瞬時接通器件,該器件能馬上管理PCB上其他器件的上電順序。因此,相對于在毫秒量級上電的微控制器,能夠在幾微秒內上電的CPLD是上電排序功能更好的選擇。

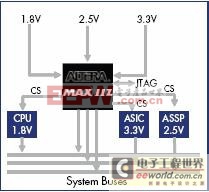

圖3所示為典型的MAX IIZ器件上電排序應用。隨著電路板密度以及電路板電源層數的增加,上電排序變得越來越復雜。MAX IIZ CPLD能夠輕松管理系統復雜程度不同的上電排序。多電源供電支持不同的器件,需要采用控制邏輯來管理每一器件的上電順序。為確保在上電期間不會出現對總線信號的意外驅動,也需要MAX IIZ器件來控制關鍵總線信號,直至上電完成。JTAG端口監視上電順序,存儲上電時的錯誤和信息。它還可以用于在調試階段設置上電排序斷點。

圖3. 利用CPLD實現上電排序

評論